Introdução

Linear Feedback Shift Register (LFSR) é um registro de deslocamento de palavras de bits, no qual o valor do bit de entrada é definido exclusivamente por alguma função com base nos valores dos bits restantes do registro antes do deslocamento. O registrador de deslocamento pode ser algum tipo de circuito elétrico composto de componentes discretos: transistores, resistores, também pode ser integrado a um microcircuito ou implementado em um programa. A adição de feedback transforma o registrador de deslocamento em um gerador de números pseudo-aleatórios, que é amplamente usado em criptografia. Neste artigo, analisaremos o princípio de funcionamento do RSLOS desde o hardware até suas diversas aplicações.

Um registrador, em geral, é um circuito que consiste em elementos de memória de um bit interconectados. Esses circuitos podem gravar, armazenar e ler dados binários de n bits. O artigo discute um tipo de registrador denominado registrador de deslocamento. Na maioria das vezes, o shift register é montado com base em D-flip-flops conectados em série, e o número desses flip-flops é igual ao número de bits n. Começamos este artigo com os princípios do D-trigger.

D-trigger

Vamos abordar brevemente o básico. Globalmente, a eletrônica pode ser dividida em duas seções: analógica e digital. A principal característica do segundo é que os sinais são definidos por níveis de tensão discretos. Além disso, existem apenas dois níveis discretos. Assim, em vez de registrar a tensão em volts, é suficiente simplesmente citar um dos dois níveis discretos. É assim que aparecem os nomes "zero" e "um". Na verdade, eles definem alguns níveis de voltagem, que podem ser qualquer coisa. Embora, na maioria dos casos, "zero" denote o nível de 0 Volts e "um" o nível de 5 V, 3,3 V, 1,8 V, 1,5 V, etc. Assim, a frase "na entrada zero, na saída um" significa: "na tensão de entrada correspondente ao nível zero, na tensão de saída correspondente ao nível um".

. , ? D- , ! .

– , .

D- – , . ,

D- , . : D (), C ( , , , clk, clock) Q (). : , , . , , .

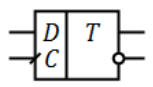

. 1 - D-

D- : C, . . . - «», «», «».

|

|

||

(D) |

(Q) |

(D) |

(Q) |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

« ». , ( ) . , . , .. . , , . , .

, . D- . , . , , . D-, .

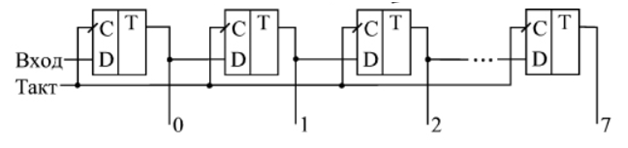

, n D-. . , , . .

? , , , . . «» . , , . ? ( ). . . , , , . . . , , . , : .

№ |

|

0 |

1 |

2 |

3 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

3 |

0 |

0 |

0 |

1 |

0 |

4 |

0 |

0 |

0 |

0 |

1 |

5 |

0 |

0 |

0 |

0 |

0 |

- . . ? , . . , , , , . .

hi - , . .

? . , , . , , 1 , . . . , .

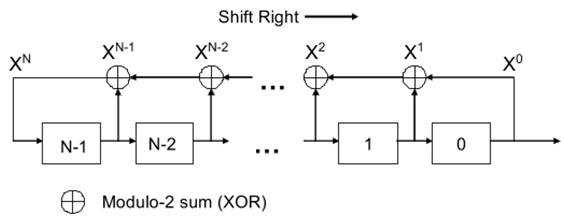

, . ? , , . n , n . , . Xi. , . . . N, Xi+N = Xi i. 2n-1, -. , , 2n-1. .

GF(2). . t + 1, (x) p:

Y(t) t. T – n :

, , . , GF(2) - : k 2k-1. . , . , . .

n |

LFSR-2 |

LFSR-4 |

2 |

2, 1 |

|

3 |

3, 2 |

|

4 |

4, 3 |

|

5 |

5, 3 |

5, 4, 3, 2 |

6 |

6, 5 |

6, 5, 3, 2 |

7 |

7, 6 |

7, 6, 5, 4 |

8 |

|

8, 6, 5, 4 |

, , . , n= 8 :

. : . . , . , , , . . : .

. . . . 2n1 , 2n2, . ., 2n1+n2+… , n1, n2, … .

. . . — 2017. — 117 .

. . . — , 2008. — 314 .

Eastlake D., Schiller J., Crocker S. Randomness requirements for security. — 2005. — 48 .