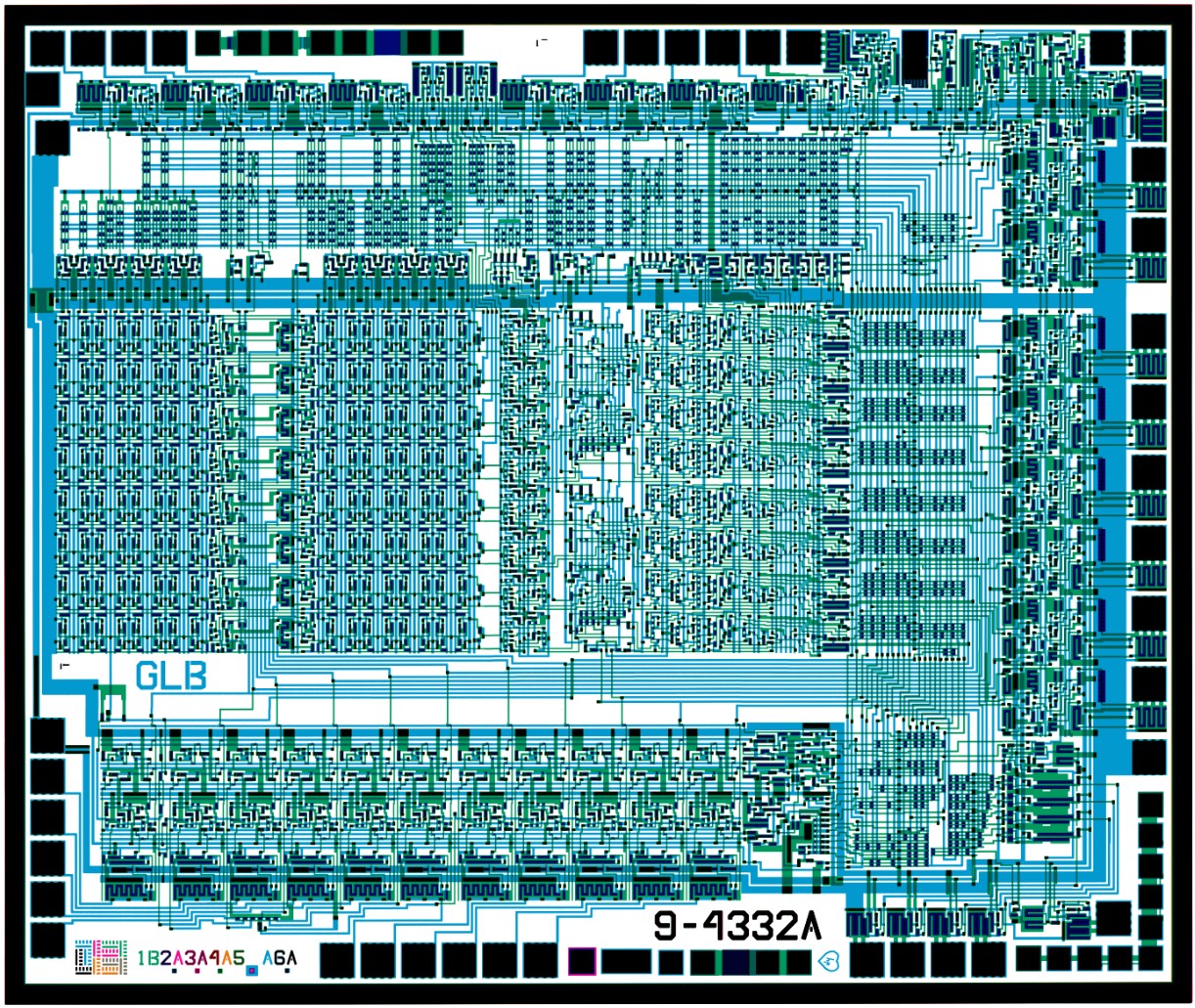

Nanoprocessador combinado com fotomáscaras. GLB à esquerda do barramento de dados são as iniciais dos desenvolvedores George Latham e Larry Bauer.

O HP Nanoprocessor é um processador quase esquecido desenvolvido pela Hewlett-Packard em 1974 (para obter detalhes, consulte The Forgotten Ones: HP Nanoprocessor , HP9825.com e The HP 9845 Project ) como um microcontrolador para vários produtos da empresa. É estranho que este processador não pudesse nem somar ou subtrair - talvez seja por isso que eles decidiram chamá-lo não de processador, mas de “nanoprocessador”. Apesar dessas limitações, o Nanoprocessor gerenciava uma variedade de dispositivos da Hewlett-Packard, desde painéis front-end e voltímetros a analisadores de espectro e terminais de aquisição de dados.

Eu determinei que o Nanoprocessador foi usado especificamente nos seguintes produtos da Hewlett-Packard: HP 9845B Spectrum Analyzers, HP 3585A , HP 3325A Synthesizer / Function Generator , HP 9885 Floppy Drive , HP 3070B Data Acquisition Terminal , HP 98034 HPIB interface para calculadora HP 9825, relógio em tempo real HP 98035 para computador HP 9825, interface do drive de filme HP 7970E , roteador HP 4262A , analisador de espectro HP 3852 , voltímetro HP 3455A... Paul-Henning Camp também me disse que o nanoprocessador foi usado no sintetizador / gerador de funções HP 3336 e no controlador de switch HP 9411. A

principal característica do nanoprocessador era seu baixo custo e alta velocidade: em comparação com o atual Motorola 6800, o nanoprocessador custava US $ 15, não US $ 360 , e lidou com tarefas de gerenciamento uma ordem de magnitude mais rápida.

É interessante que o concorrente do Nanoprocessador em seu desenvolvimento foi o Motorola 6800, e não o processador da Intel. O principal que o Nanoprocessador podia se orgulhar era a velocidade: funcionava a 4 MHz, sendo que o 6800 funcionava a 1 MHz. Ambos os processadores levaram 2 ciclos de clock para executar uma instrução básica, enquanto o 6800 levou até 7 ciclos de clock para executar instruções mais complexas.

Os desenvolvedores do Nanoprocessador fizeram uma comparação de velocidade e sugeriram que o Nanoprocessador podia ler seis vezes mais rápido que o 6800 e lidar com interrupções mais de 16 vezes mais rápido. No entanto, foi então assumido que o Nanoprocessador operaria a 5 MHz, e o chip real ficou um pouco aquém dessa barra com seus 4 MHz. O preço preliminar do Nanoprocessador foi chamado de $ 15 contra $ 360 para o Motorola 6800.

Não concordo que o Nanoprocessador possa ser chamado de microcontrolador, pois usa uma ROM externa com um programa, enquanto um microcontrolador geralmente tem tudo, incluindo a ROM, em um chip (neste aspecto parece Intel 4004). No entanto, em quase todos os aspectos, o nanoprocessador se assemelha a um microcontrolador: ele é projetado para uso embutido, sua arquitetura Harvarde o conjunto de instruções é otimizado para E / S, ele executa programas de ROM com armazenamento mínimo de dados.

Quanto aos computadores que não podiam somar - o computador IBM 1620 do tamanho de uma mesa de 1959 não tinha uma operação de adição, mas usava uma tabela de resultados para isso. Seu codinome era CADET, e as pessoas o decifraram brincando como "Não é possível adicionar, nem mesmo tenta" [não pode adicionar e nem tentar].

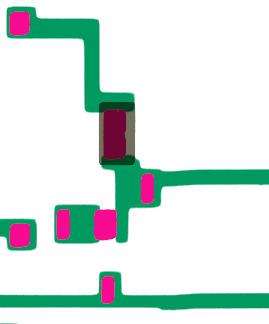

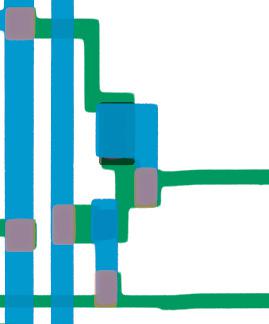

Recentemente, o designer de chips Larry Bauer publicou seis fotomáscaras usadas para produzir o Nanoprocessador, junto com detalhes de seu design. As fotomáscaras foram limpas e digitalizadas no The CPU Shack e, em seguida, limpas por Antoine Berkovichi (o arquivo PSD de 122 MB pode ser baixado do link) A imagem composta das fotomáscaras abaixo mostra os circuitos internos do IC. A camada azul é a camada de metal superior do chip, a verde é a camada de silício inferior. Quadrados pretos em todo o perímetro - 40 locais para comunicação com contatos externos do IC. Usei essas fotomáscaras para fazer a engenharia reversa do processador para entender seu circuito simples, mas inteligente, semelhante ao RISC.

O nanoprocessador se assemelha a um processador Reduced Instruction Set Computer (RISC) em muitos aspectos, embora tenha surgido vários anos antes de tal conceito. Em particular, o nanoprocessador é projetado com um sistema de instrução simples, todas as instruções são executadas em um ciclo de clock (após o clock de amostragem), o conjunto de registradores é grande e ortogonal e o endereçamento é simples. Essas características inerentes do RISC resultaram em velocidades de clock mais altas em comparação com processadores mais complexos.

O nanoprocessador foi desenvolvido em 1974, ao mesmo tempo em que os processadores clássicos Intel 8080 e Motorola 6800 foram anunciados. No entanto, o processo de fabricação do nanoprocessador de silício demorou vários anos - eles usavam transistores de porta de metal em vez de silíciodesenvolvido no final dos anos 1960. A diferença parece confusa, mas as portas de silício eram melhores em vários aspectos . Primeiro, eles são menores, mais rápidos e mais confiáveis. Em segundo lugar, eles tinham uma camada de polissilício com condutores diferentes de metal; como resultado, o layout do chip era quase duas vezes mais denso. Terceiro, os transistores de porta de metal exigiam uma fonte de alimentação adicional de + 12 V. O processador Intel 4004 usava portas de silício em 1971, então estou surpreso que a HP ainda usasse metal em 1974.

Dadas essas limitações, estou impressionado com a densidade da fiação do Nanoprocessador - uma camada de metal, sem polissilício. Procurei outros chips de portão de metal e sua fiação é terrivelmente ineficiente - há mais condutores do que transistores. Ao mesmo tempo, as cadeias de nanoprocessadores são localizadas de forma eficiente e não desperdiçam espaço extra.

A tecnologia de nanoprocessador ultrapassou o Intel 8080 e o Motorola 6800 em uma coisa: ela usava transistores pull-up no modo de depleção, mais avançados do que os transistores no modo aprimoramento usados em 8080 e 6800 A primeira tecnologia fornece portas lógicas que são mais rápidas e consomem menos, mas exigem uma etapa de produção adicional. No Nanoprocessador, Photomask # 3 (cinza) foi usado nesta etapa. Processadores como o MOS Technology 6502 e o Zilog Z80, transistores pull-up com seu próprio canal, permitiam que operassem com uma tensão, não três. Infelizmente, o nanoprocessador ainda exigia tensões diferentes devido ao transistor de porta metálica.

Uma característica muito estranha do Nanoprocessador é a voltagem de polarização alternada do substrato. Por razões de velocidade, muitos microprocessadores dos anos 1970 aplicaram voltagem negativa ao wafer de silício, com -5 V aplicado através de um contato de polarização. O nanoprocessador tem um pino de polarização, mas é estranho que a voltagem de polarização varie de chip para chip, de -2 V a -5 V. Durante a produção, a voltagem desejada foi escrita no chip manualmente (veja abaixo). Cada nanoprocessador teve que ser instalado com um resistor correspondente para obter a tensão correta. Se o nanoprocessador foi alterado na placa, o resistor teve que ser alterado também. O viés variável parece uma falha de fabricação - não consigo imaginar a Intel fazendo isso nos processadores.

Os primeiros chips DRAM e microprocessadores geralmente exigiam três tensões de alimentação: +5 V (Vcc), +12 V (Vdd) e -5 V (Vbb) tensão de deslocamento. No final da década de 1970, melhorias na tecnologia de fabricação tornaram possível o uso de uma única tensão. O microcontrolador Intel 8080 de 1974 usava transistores de canal induzido que exigiam três voltagens, mas uma versão aprimorada do 8085 (1976) usava um transistor com seu próprio canal e era alimentado por uma única voltagem de + 5 V. Desde o final dos anos 1970, muitos microprocessadores usaram bombas de carga. localizado no chip para gerar uma tensão de polarização negativa.

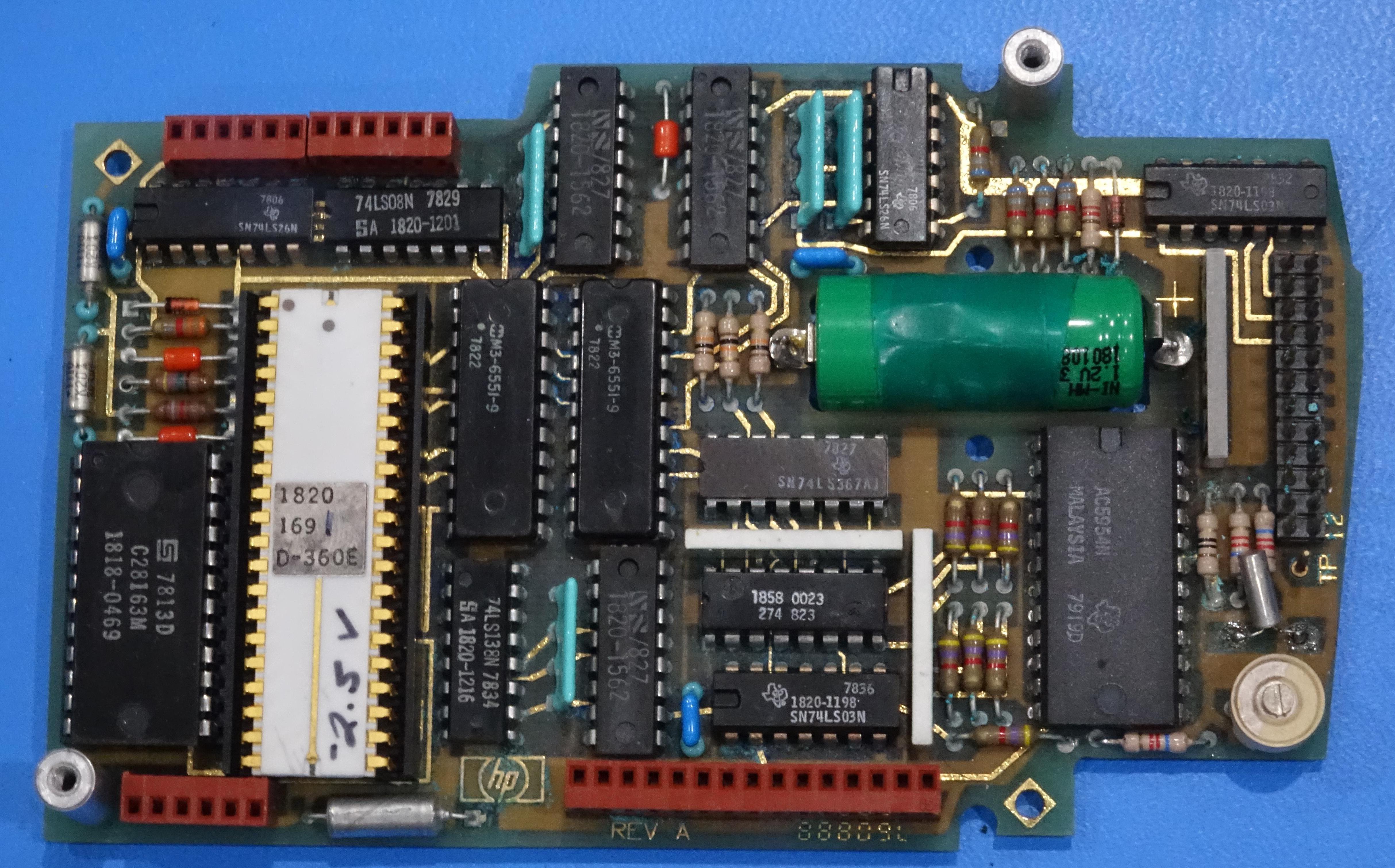

Número da peça do nanoprocessador HP 1820-1691. Observe a tensão escrita à mão: -2,5 V. O último dígito do número da peça (1) também é escrito à mão e representa a velocidade do chip.

Como a maioria dos processadores daquela época, o Nanoprocessador era de 8 bits. Ele não usou memória de acesso aleatório, no entanto, mas executou o código de uma ROM externa de 2 KB. Ele tinha 16 registradores de 8 bits - mais do que a maioria dos processadores e o suficiente para compensar a falta de memória em muitos aplicativos. Em termos de número de transistores, o Nanoprocessador é mais complexo do que Intel 8008 (1972) e ligeiramente mais fácil do que 6800 (1974) ou 6502 (1975).

De acordo com meus cálculos, o Nanoprocessador tem 4639 transistores. O decodificador de instrução é composto de pares de pequenos transistores com base em considerações de localização. A combinação desses pares resulta em 3829 transistores únicos. Destes, 1061 são pull-ups e 2668 estão ativos. Para efeito de comparação, o 6502 tinha 4237 transistores, dos quais 3218 estavam ativos. O 8008 tinha 3500 transistores, enquanto o Motorola 6800 tinha 4100.

Mas sua arquitetura usa transistores para uma finalidade diferente da desses processadores. O nanoprocessador não possui uma ALU, mas, em vez disso, possui um grande conjunto de registros ocupando a maior parte da área do dado. O nanoprocessador tem 48 equipes, significativamente menos do que o 6800 com 72 equipes. No entanto, o Nanoprocessor tem operações úteis de definir, redefinir e verificar bits que os processadores mencionados não tinham. O nanoprocessador oferece suporte ao acesso a registradores por índice, mas não possui modos de endereçamento complexos como outros processadores.

Os primeiros microprocessadores não tinham operações de definição, redefinição e verificação de bits (embora possam ser implementadas por meio de AND e OR). O Z80 (1976) adicionou operações bit a bit, mas elas tinham dois bytes cada e eram muito mais lentas do que o Nanoprocessador.

O diagrama de blocos abaixo mostra a estrutura interna do Nanoprocessador. O principal recurso de I / O é o "I / O Instruction Device Select" de 4 bits, que permite que 15 dispositivos recebam comandos de I / O. Em outras palavras, os pinos selecionados determinam qual dispositivo de E / S está lendo ou gravando nos barramentos de dados. Os circuitos externos usam esses sinais para tudo que um aplicativo específico precisa - armazenar dados em uma trava, enviar para outro sistema, ler valores. Ainda mais I / O é fornecido por meio de pinos de I / O de controle direto (pinos GPIO), adequados para entrada e saída. Se esses pinos não estiverem conectados a circuitos externos, eles atuam como sinalizadores de bit de conveniência; O nanoprocessador pode definir um valor e depois lê-lo.Na ausência de um módulo de lógica aritmética, o módulo de lógica de controle executa operações de incremento, decremento, deslocamento e operações de bit no somador.

Diagrama de bloco do manual do usuário do nanoprocessador

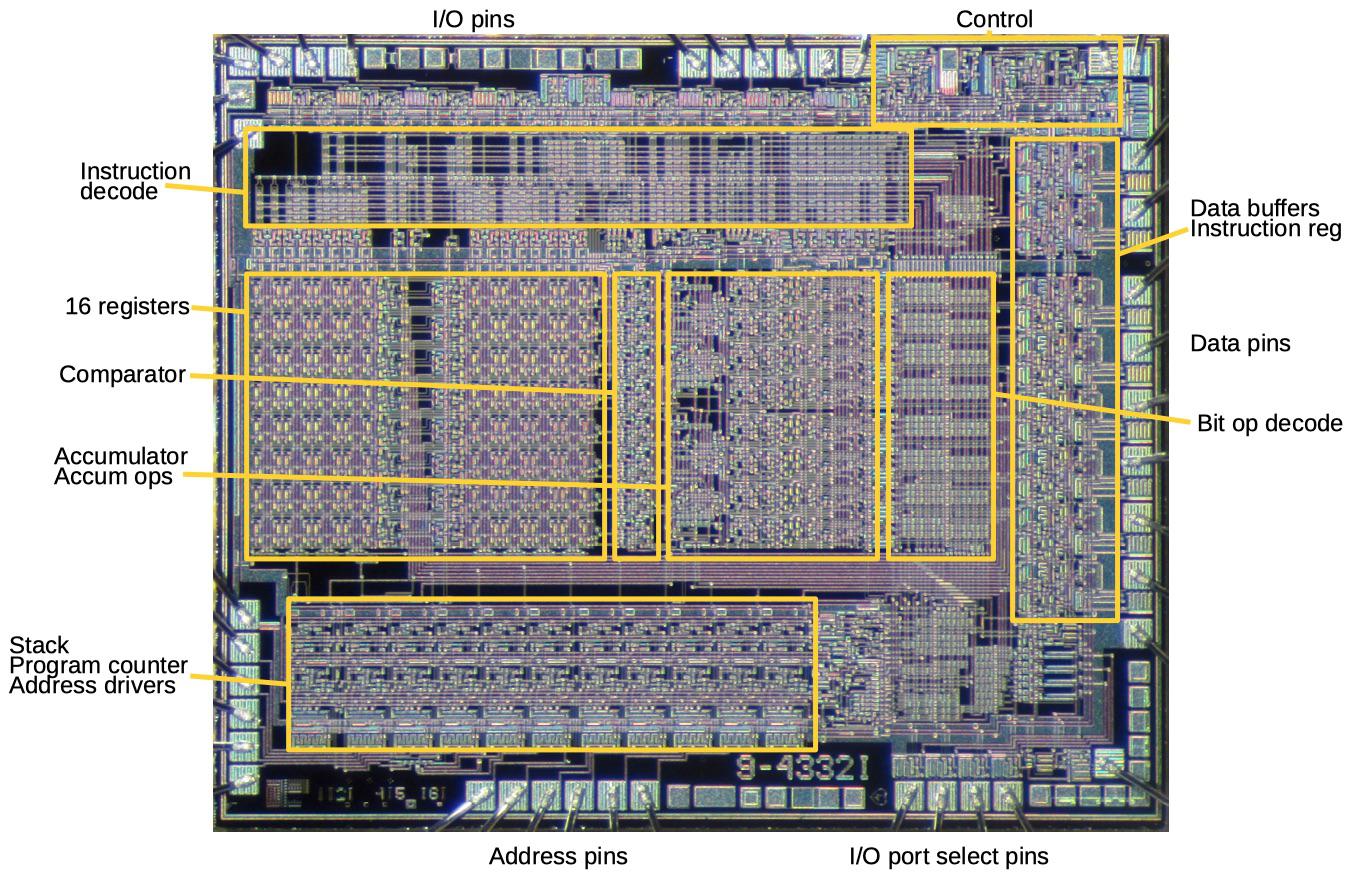

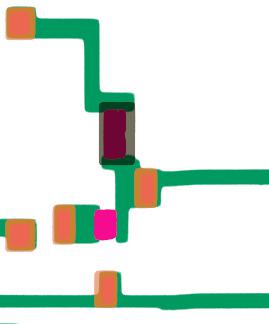

Fiz a engenharia reversa do Nanoprocessador com base em fotomáscaras e mapeei a colocação dos blocos funcionais na matriz. O maior elemento é um conjunto de 16 registros à esquerda do centro. À direita está o comparador e somador, junto com seus circuitos de incremento, decremento, deslocamento e complemento. O decodificador de instruções ocupa a maior parte do espaço acima e à direita do comparador de bateria. A parte inferior do chip é ocupada principalmente por um contador de instruções de 11 bits, bem como por uma pilha de interrupções de entrada única e uma pilha de sub-rotinas. As cadeias de controle implementam a sincronização de comando mais simples: um ciclo de extração é seguido por um ciclo de execução. A maioria dos microprocessadores tem circuitos de controle que ocupam uma parte significativa do chip, mas os circuitos de controle do nanoprocessador são pequenos blocos.

O nanoprocessador segue seu modelo de execução de instruções em um ciclo, mesmo para instruções de byte duplo: o segundo byte é solicitado durante o ciclo de execução, de modo que o tempo total de execução do comando não muda.

Componentes funcionais do nanoprocessador HP

Compreender as máscaras fotográficas

O chip foi fabricado com seis fotomáscaras, cada uma delas utilizada para produzir uma das camadas processadoras por meio da fotolitografia . A foto abaixo mostra máscaras fotográficas. Cada uma é uma folha Mylar de 47,2 x 39,8 cm. São fotomáscaras ampliadas 100x usadas para produzir um cristal de silício de 4,72 x 3,98 mm (33% menor que o cristal de 6800). Cada wafer de silício de 3 polegadas continha cerca de 200 CIs, que foram produzidos simultaneamente, depois testados, cortados e colocados em um pacote.

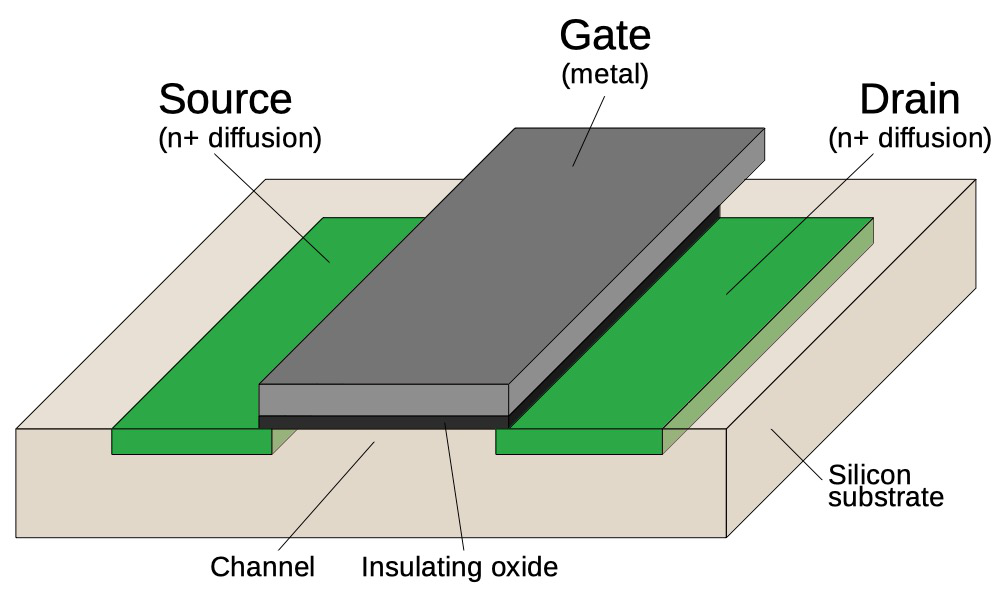

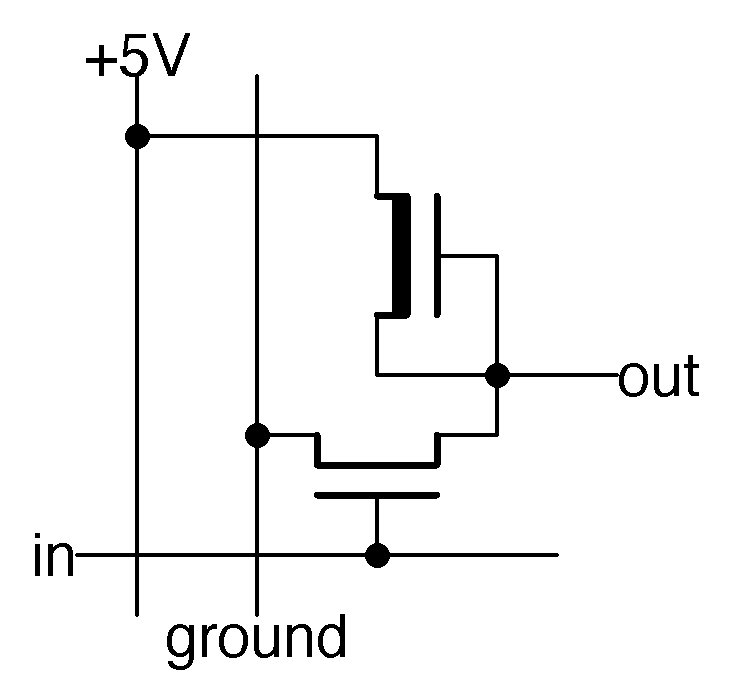

Para explicar o papel das máscaras, começarei descrevendo a estrutura MOS da porta de metal usada no Nanoprocessador. No diagrama abaixo, duas seções de silício (verde) são tornadas condutoras com a ajuda de impurezas e formam a fonte e o dreno do transistor. Uma tira de metal entre eles forma uma porta, separada do silício por uma fina camada de óxido isolante (daí o nome da estrutura - Metal, Óxido, Semicondutor). O transistor pode ser considerado uma chave controlada pelo portão. Além disso, a camada de metal fornece o método principal para conectar os componentes do IC a condutores, embora alguns condutores também passem pela camada de silício.

Esquema de uma estrutura MOS com uma porta de metal

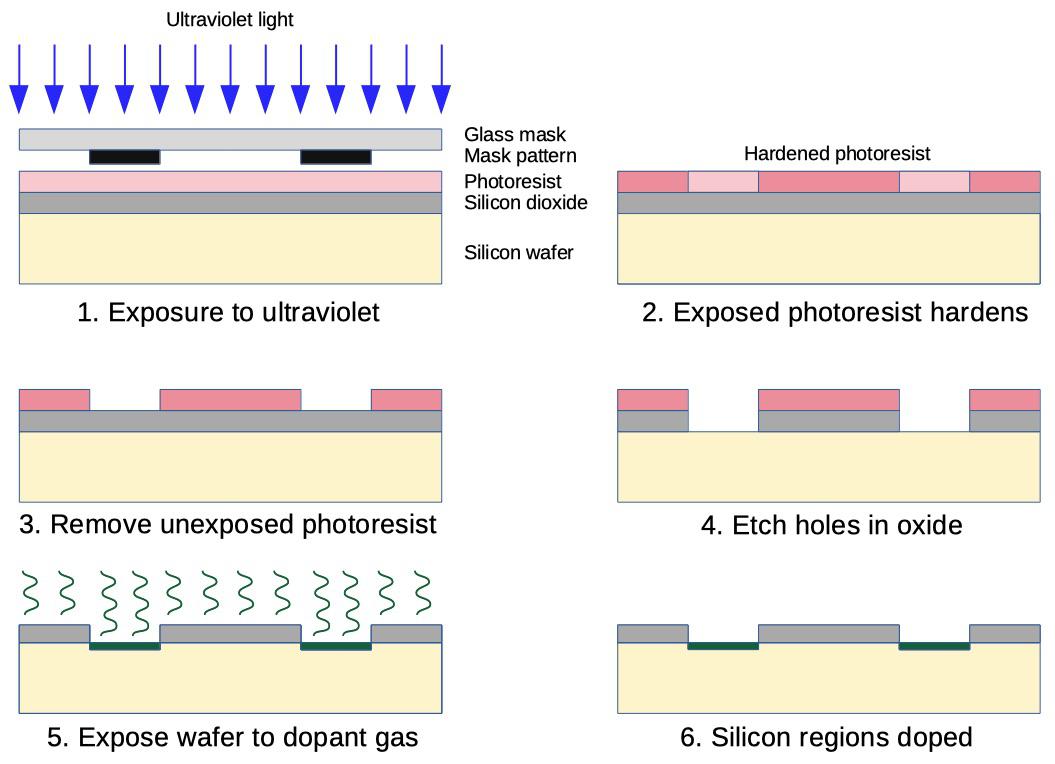

As fotomáscaras são uma parte fundamental do processo de fabricação de CI, pois localizam os componentes. O diagrama abaixo mostra como as impurezas são adicionadas a algumas áreas de silício usando fotomáscaras. Primeiro, uma camada de óxido isolante é formada no substrato de silício, em seguida, um fotorresiste fotossensível é adicionado... A luz ultravioleta (1) polimeriza e cura o fotorresiste em todos os lugares, exceto onde a máscara bloqueia a passagem da luz (2). Em seguida, o fotorresiste macio que não foi exposto à radiação ultravioleta é removido (3). O substrato é exposto ao ácido fluorídrico, que remove a camada de óxido onde não está protegida pelo fotorresiste (4). Orifícios aparecem no óxido que correspondem ao padrão da fotomáscara. Em seguida, o substrato é exposto a um gás quente que penetra em áreas desprotegidas do silício e altera suas propriedades condutoras (5). Esse processo gera pequenas áreas de silício com impurezas, correspondentes à figura da fotomáscara (6). Outras fotomáscaras são usadas para outras etapas de produção, mas usam o mesmo processo usando um fotorresiste.

Como adicionar impurezas às regiões de silício usando fotomáscaras Vou

ampliar uma seção do Nanoprocessador para mostrar como um circuito é formado a partir de seis fotomáscaras (que é um inversor que altera o valor binário que chega à entrada). Usando a primeira fotomáscara e o processo de fotolitografia descrito acima, as porções de silício são feitas condutoras. As áreas marcadas em verde com impurezas formarão as fontes / drenos do transistor ou a junção de componentes.

A primeira fotomáscara cria manchas de silício condutor

O cristal é então coberto com uma camada de óxido isolante. A segunda fotomáscara (roxa) é usada para fazer buracos no óxido que expõem o silício subjacente. Esses orifícios podem ser usados para criar as portas do transistor, bem como a conexão de condutores de metal e silício.

A segunda fotomáscara cria orifícios na camada de óxido,

a terceira fotomascara (cinza) expõe áreas para implantação de íons que alteram as propriedades do silício e, consequentemente, do transistor. Isso transforma o transistor superior em um transistor canalizado que aumenta a saída da porta lógica.

A terceira fotomáscara (cinza) cria impurezas no silício do transistor superior

O silício é então revestido com uma fina camada adicional de óxido isolante para formar os óxidos de porta para o transistor. A quarta fotomáscara (laranja) remove esse óxido das áreas que se tornarão contatos entre o silício e a camada de metal. Após esta etapa, a maior parte do cristal é coberta com um óxido isolante espesso. Acima das portas do transistor (roxo), a camada de óxido é muito fina, e possui orifícios para contatos da fotomáscara atual (laranja).

A quarta fotomáscara cria buracos no óxido

A quinta máscara fotográfica (azul) é usada para criar condutores de metal na parte superior - para isso, uma camada uniforme de metal é primeiro aplicada e as partes desnecessárias são então removidas. Onde a quarta fotomáscara criou buracos no óxido, a camada de metal entra em contato com o silício e forma um contato condutor. Onde a terceira máscara criou uma fina camada de óxido, a camada de metal forma a porta do transistor entre as duas seções de silício. Finalmente, todo o substrato é coberto com uma camada vítrea protetora. A sexta máscara fotográfica é usada para criar orifícios nesta camada acima dos contatos nas bordas do chip. Depois de cortar todo o substrato em cristais individuais, um fio de solda é soldado a esses contatos, conectando-os aos contatos externos.

A quinta máscara fotográfica cria um layout metálico

O diagrama abaixo mostra como este circuito forma um inversor com dois transistores. Os dois símbolos do transistor correspondem aos dois transistores obtidos com a fotomáscara. Na ausência de um sinal de entrada, o transistor superior (conectado a +5 V) aumenta a saída. Quando o sinal de entrada está alto, ele liga o transistor inferior. Isso conecta a tomada ao aterramento, puxando a tomada para baixo. Assim, o circuito inverte o sinal de entrada.

Circuito inversor N-MOS correspondendo aos modelos acima

Embora os diagramas acima mostrem um único inversor, essas etapas usam máscaras fotográficas para criar um processador completo com todos os transistores 4639. O diagrama abaixo mostra uma parte maior da matriz, onde dezenas de transistores formam portas e circuitos mais complexos. Notei uma coisa tocando em uma das fotomáscaras - um coração minúsculo com as letras HP dentro, sob o número do chip.

O nanoprocessador tem dois números de peça diferentes. 1820-1691 denota uma versão de 2,66 MHz e 1820-1692 denota uma versão de 4 MHz. O último dígito foi escrito manualmente em cada chip após ser verificado no caso. O número da peça não está relacionado ao número do chip 9-4332A na matriz.

Desenhos de chips

Como o Nanoprocessor gerencia o relógio

Para entender como o nanoprocessador era usado na prática, fiz engenharia reversa do código do módulo de relógio HP 98035. O módulo se conectou a um computador desktop HP 9825 e serviu como um relógio de tempo real, e também pode medir intervalos e acionar eventos periódicos com precisão de milissegundos. O circuito do módulo de relógio era bastante incomum. Para manter a hora atual quando o computador está desligado, o módulo de relógio foi construído com base em um chip de relógio digital com uma bateria sobressalente. O chip do relógio não era projetado para o controle do computador, o que causava transtorno: gerava sinais de 7 segmentos para controlar os LEDs e era configurado com três botões. Para descobrir a hora, o Nanoprocessador teve que converter a saída do display de 7 segmentos de volta em números.Para definir o tempo do nanoprocessador, você tinha que emular a sequência correta de pressionamentos de botão.

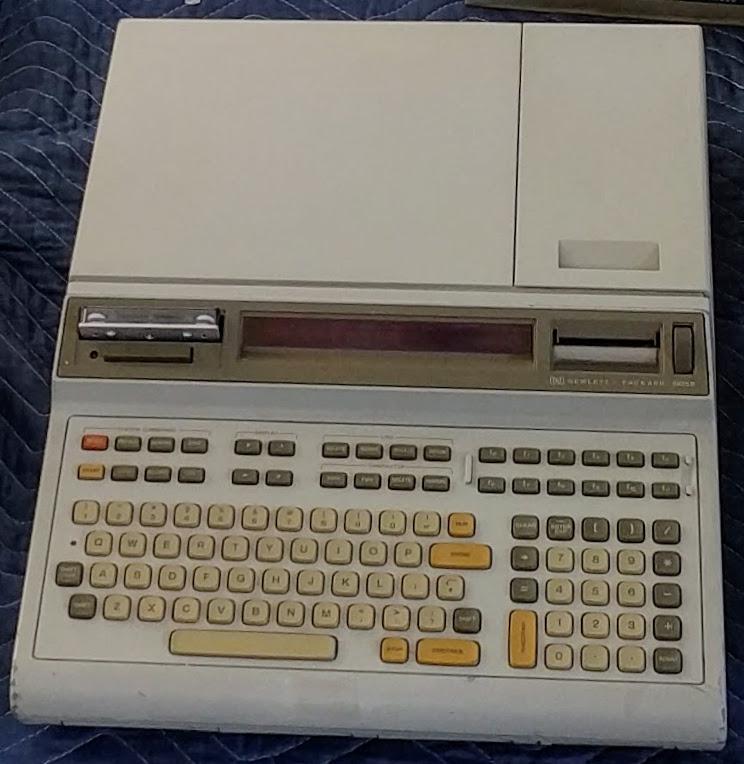

O HP 9825 era um computador desktop de 16 bits com suporte para uma linguagem semelhante ao BASIC. Introduzido em 1976, cinco anos antes do IBM PC, era um sistema bastante avançado para a época. Na parte traseira, ele tinha três conectores para adicionar módulos, como um módulo de relógio em tempo real.

HP 9825 com display LED, unidade de fita e impressora

Para economizar energia, o chip de relógio da Texas Instruments é implementado em lógica de injeção integrada (I2L). Os chips de baixa potência usariam CMOS hoje, mas isso era raro naquela época. O I2L foi construído sobre transistores bipolares, semelhantes ao TTL, mas usando circuitos diferentes com alta densidade e baixo consumo de energia. Talvez fosse um chip X-902 em um pacote DIP.

Nanoprocessador (chip branco) como parte do módulo de relógio HP. À esquerda dele está uma ROM de 2 KB. À direita estão dois chips de memória de 256 bits x 4. O chip do relógio da Texas Instruments é um grande chip preto sob a bateria NiCad verde. O

computador controlava o módulo do relógio enviando-lhe sequências ASCII de caracteres como "S 12: 07: 12: 45: 00", que deveria ter definido a hora para 12:45:00 7 de dezembro (ou 12 de julho na notação europeia). Os diversos timers de intervalo, alarmes e contadores do módulo foram iniciados de forma semelhante, através de comandos como "Unidade 2 Período 12345". O módulo suportava 24 comandos e o nanoprocessador precisava reconhecê- los .

Aqui está um trecho de código com engenharia reversa da ROM da placa do relógio. Este é o código do manipulador de interrupção que incrementa o cronômetro e a data a cada segundo. O código determina o número de dias em um mês para que saiba quando mudar o mês para o próximo. Colunas - valores de byte, comandos e minhas explicações. Este código pega o número do mês (01-12 BCD), armazena-o no acumulador e retorna o número de dias do mês (28, 30 ou 31 BCD) no registro 0. Nada mal para 16 bytes de código, apesar de ignorar anos bissextos. Como ele trabalha? Para meses após 7 (julho), ele subtrai 1. Então, se o mês for ímpar, então ele tem 31 dias, e se for par, 30 dias.Para processar fevereiro, o código limpa o bit de 1 mês. Se o mês chegar a 0 (fevereiro), terá 28 dias.

d0 STR-0 (7) 0.

07

0c SLE , <= 0.

03 DED 1

5f NOP

d0 STR-0 (0x31) 0

31

30 SBZ-0 , 0 0

81 JMP-1 0x1c9 ( )

c9

a1 CBN-1 1

d0 STR-0 (0x30) 0

30

0f SAN , 0

d0 STR-0 (0x28) 0

28

Você pode ver pelo código que, mesmo que um processador sem uma operação de adição pareça inútil, as operações bit a bit e o incremento / decremento do nanoprocessador permitem mais cálculos do que você possa imaginar.

No código, me deparei com um lugar onde preciso adicionar dois números BCD e formar um byte. Isso era feito por um ciclo que diminuía um número e aumentava outro. Quando o primeiro número alcançou zero, o segundo obteve sua soma. Assim, mesmo sem ALU, a adição pode ser realizada, ainda que lentamente.

Você também pode ver que o código do nanoprocessador é compacto e eficiente. Você pode fazer muito em um byte, o que em outros processadores leva vários bytes. Um grande conjunto de registradores do Nanoprocessador permite evitar a troca de dados enfadonha de um lado para outro. Embora alguns considerem o Nanoprocessador mais uma máquina de estado do que um microprocessador, isso seria um eufemismo das capacidades e do papel do Nanoprocessador.

Embora o Nanoprocessador não tenha ALUs ou comandos de memória de acesso aleatório, eles podem ser conectados como dispositivos de E / S adicionais. O relógio possui uma memória de acesso aleatório de 256 bytes que armazena os valores dos contadores e temporizadores, cujo acesso é organizado através das portas de E / S. Outros produtos adicionaram ALUs para dar suporte a operações aritméticas.

O diagrama da placa do relógio mostra como dois chips de RAM 256x4 estão conectados ao Nanoprocessador. A porta I / O do nanoprocessador seleciona um pino e se conecta ao "decodificador 3-8" U5, que emite sinais separados para cada uma das portas I / O. Três deles vão para os pinos de controle do chip RAM, e um controla os chips das travas de dados U9 e U10, que armazenam os dados gravados.

Todas as portas de E / S usam o barramento de dados do nanoprocessador (parte superior) para trocar dados, portanto, o barramento se conecta aos pinos de endereço dos chips de RAM e aos pinos de dados. Para leitura, o endereço da memória é escrito nos chips por meio de uma porta de E / S e, em seguida, os dados são lidos da memória por outra porta. Em ambos os casos, os valores passam pelo barramento de dados e o sinal do "Decodificador 3-8" indica o que fazer com os valores. Para gravação, a primeira operação de E / S armazena o valor do byte nas travas e, em seguida, a segunda operação de E / S envia o endereço para os chips de memória. Isso pode soar como uma abordagem desajeitada no estilo de máquina de Goldberg , mas na prática funciona bem e a leitura / gravação pode ser feita com dois bytes de instruções.

Muitos processadores, como o 6502, usam I / O mapeados na memória - os dispositivos são mapeados para o espaço de endereço da memória e acessados por meio de operações de leitura / gravação. O nanoprocessador funciona ao contrário, conectando memória em uma porta de E / S e acessando-a por meio de operações de E / S.

Ao adicionar ALUs, uma abordagem semelhante é usada- como no voltímetro HP 3455A usando dois nanoprocessadores. O voltímetro usa dois chips 74LS181 ALU para implementar uma ALU de 8 bits, que ele usa para escalar os valores e calcular a porcentagem de erro. Duas portas de saída fornecem argumentos e uma define uma operação. O resultado de 8 bits é lido da porta e o processador lê a transferência por meio do pino GPIO (faz você se perguntar se era mais fácil usar um processador com suporte aritmético).

Resultado

Nanoprocessador é um processador incomum. À primeira vista, até me pareceu um "processador falso", devido à falta de operações aritméticas básicas. O chip é baseado em tecnologia obsoleta de porta de metal que ficou atrás de outros microprocessadores por vários anos. O mais estranho é que cada chip exigia sua própria voltagem, que era gravada manualmente no case, o que indica as dificuldades com qualidade estável na produção. No entanto, o nanoprocessador no papel de um microcontrolador funcionou rapidamente, muito mais rápido do que outros processadores modernos. A Hewlett-Packard usou o nanoprocessador em muitos produtos nas décadas de 1970 e 1980, em funções mais sofisticadas do que se poderia esperar.

Embora o Nanoprocessador tenha sido esquecido há muito tempo, e nem mesmo escrito sobre ele na Wikipedia, as fotomáscaras publicadas recentemente por seu criador lançaram luz sobre este canto incomum da história do processador.