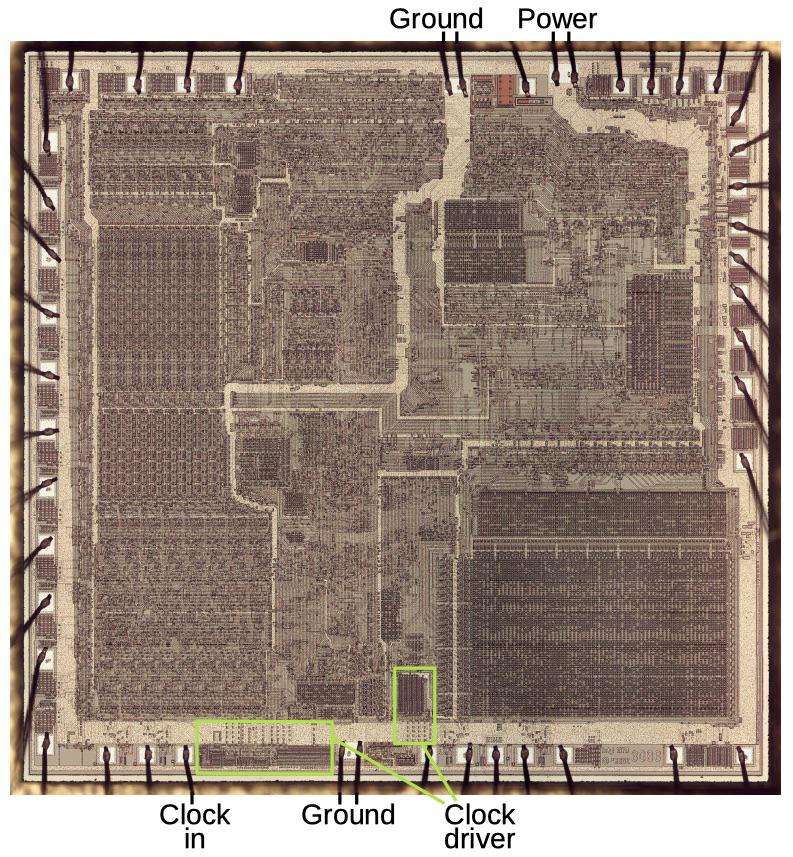

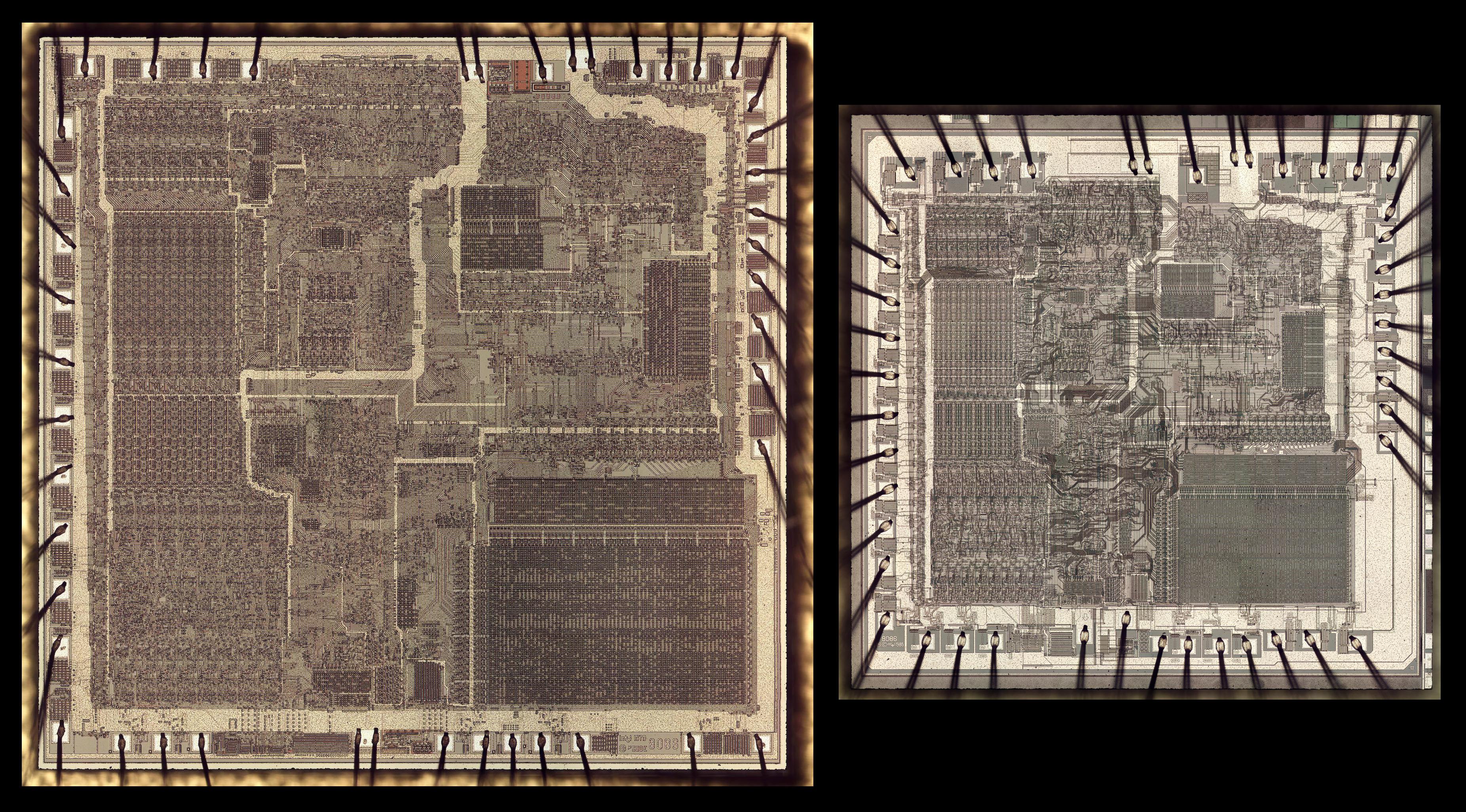

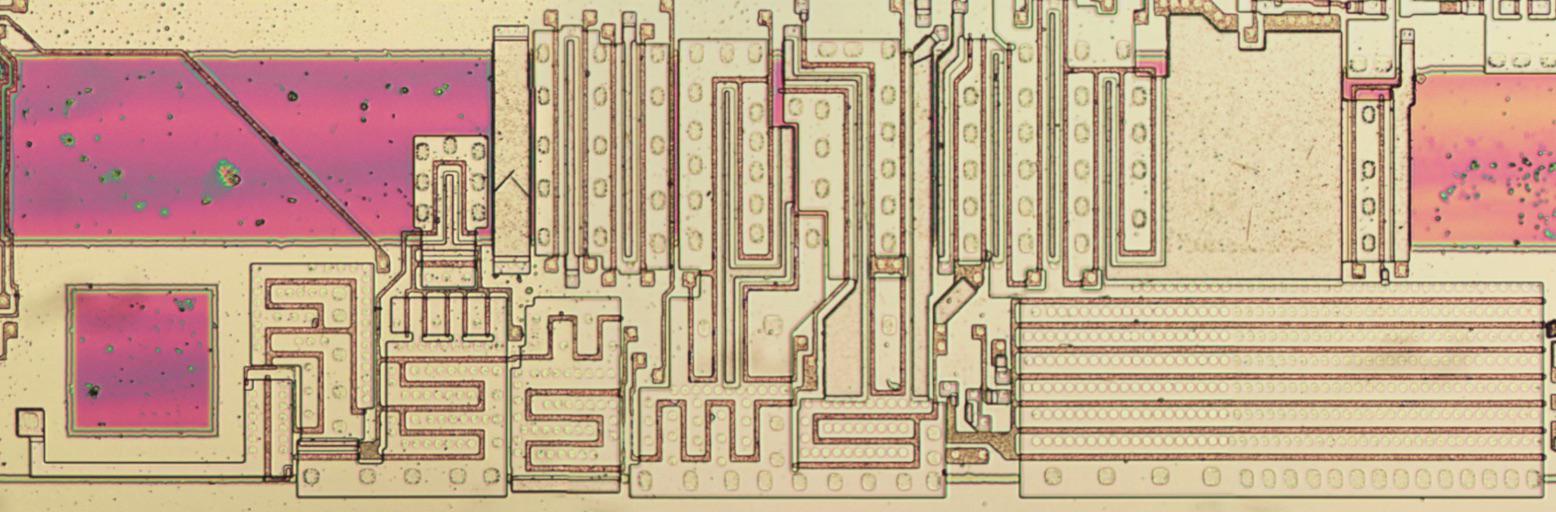

A foto abaixo mostra um cristal 8086 sob um microscópio. Uma camada de metal é visível no topo do chip, sob a qual um substrato de silício e uma camada de polissilício com condutores estão ocultos. Ao longo da parte externa do perímetro do cristal, um minúsculo fio de ligação conecta as almofadas do cristal às pernas externas. No 8086, o power pad está na parte superior e os pads estão na parte superior e inferior. Cada um deles possui dois fios para soldar, o que dobra a corrente suportada. Caminhos de metal largos são visíveis, estendendo-se das bases de alimentação e aterramento. Eles distribuem energia pelo chip.

Foto do cristal 8086, onde você pode ver o ponto de alimentação (superior) e os contatos de aterramento (superior e inferior). Os circuitos de temporização estão localizados na parte inferior.

Existem dois sinais de clock internos responsáveis pela sincronização no 8086. Um oscilador externo alimenta sinais de relógio para o 8086 por meio do teclado de relógio de entrada abaixo. O gerador de relógio interno fornece dois sinais de relógio de alta corrente com base em sinais externos. Observe que o driver do relógio ocupa uma grande área no chip.

Neste artigo, descreverei como o 8086 redireciona os sinais de energia e clock em todo o chip e como o circuito do clock gera os pulsos de clock necessários.

Distribuição de poder

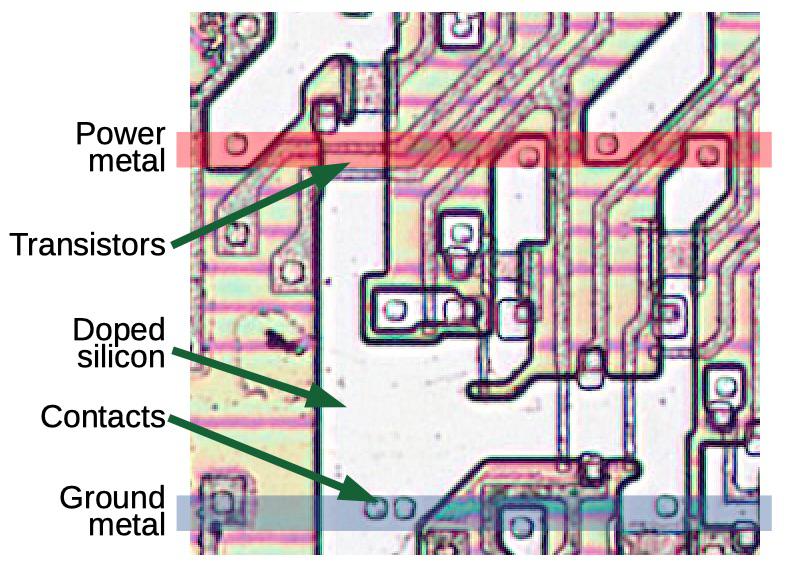

8086 consiste em três camadas, cada uma das quais pode acomodar condutores. A camada de metal na parte superior é melhor para isso devido à baixa resistência do metal. Sob o metal há uma camada de condutores de polissilício, consistindo de um tipo especial de silício. A resistência do polissilício é maior do que a do metal, mas ainda pode ser usado para transmitir sinais pelo chip. Os transistores são formados no substrato de silício. A resistência do silício é relativamente alta, então ele só é usado para transmitir sinais em distâncias curtas - por exemplo, dentro de um portão.

A distribuição de energia em um chip como o 8086 é um quebra-cabeça topológico. Devido à sua baixa resistência, a camada de metal permanece a única camada útil na prática para fiação de força e aterramento. Quase todas as portas do chip devem ser alimentadas com energia e aterramento. E como o chip tem uma camada de metal, a força e o aterramento não podem se cruzar.

Quase todas as portas no chip precisam de energia e aterramento porque a porta MOS padrão requer aterramento para sua rede pull-down e energia para seu resistor pull-up. No entanto, existem algumas exceções. 8086 usa portas lógicas dinâmicas, especialmente em ALU - para velocidade. Essas portas são atraídas para cima pelo sinal de sincronização, portanto, não precisam de uma fonte de alimentação direta. O 8086 também usa várias portas XOR nos transistores de passagem, que são puxados para baixo pelo sinal de entrada, de forma que não precisam de aterramento.

O microcódigo ROM forma uma grande seção do chip que não precisa de energia, apenas aterrada. Isso ocorre porque cada linha de ROM é implementada como uma porta NOR muito grande e a força que a puxa está localizada na borda direita. Portanto, todas as portas ROM têm alimentação e aterramento, embora pareça que a ROM não tem uma conexão de alimentação.

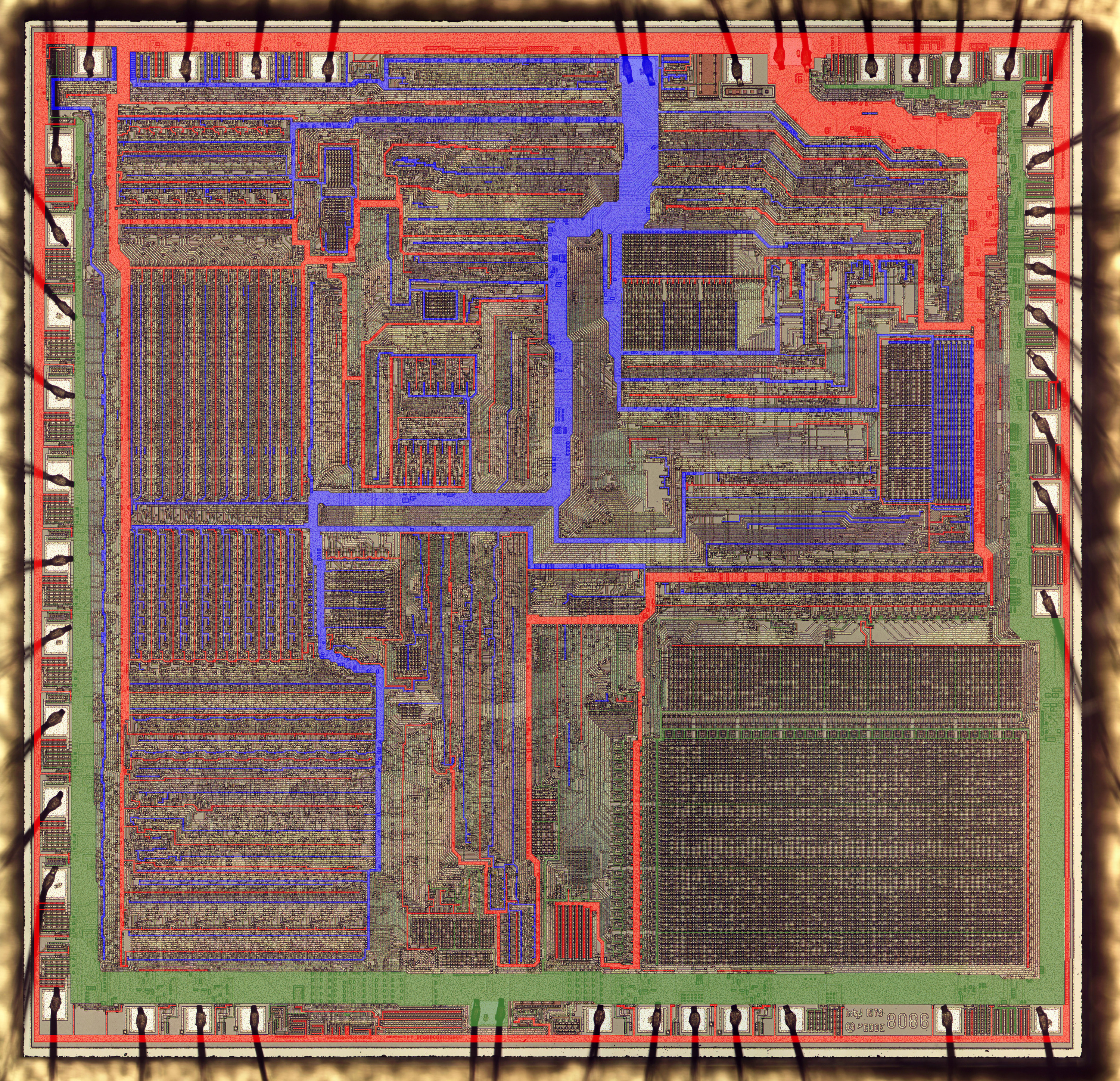

O diagrama abaixo mostra os condutores de metal no 8086. A fonte de alimentação conectada ao pino de alimentação na parte superior é mostrada em vermelho. Um poderoso ramo de comida desce e para a direita e então se divide em muitos ramos. A energia também corre ao longo da borda de todo o chip, fornecendo energia aos pinos de E / S.

Com ICs, muitas vezes acontece que a alimentação e o aterramento estão localizados em cantos opostos ou em lados opostos do chip. Esse arranjo torna mais fácil rotear trilhas de energia e de solo que não se cruzam. O 8086 tem um posicionamento um pouco incomum de alimentação e aterramento em pinos diagonalmente opostos e o segundo aterramento mais próximo do pino de alimentação. As redes de energia e as terras no chip se ramificam como árvores. Essas redes se ramificam e, como dedos entrelaçados, alcançam todas as partes do chip.

Alimentação (vermelho) e aterramento (azul, verde) na camada de metal do chip

Existem dois contatos de aterramento. Os trilhos marcados em azul se conectam ao pino de aterramento superior e os verdes ao inferior. Os caminhos de solo marcados em azul mostram uma ramificação espessa para baixo através do centro do chip e se ramificando de forma intrincada em todas as direções. As pistas verdes seguem ao longo dos lados inferior esquerdo e direito do chip, suportando os pinos de E / S e conectando-se ao microcódigo ROM no canto inferior direito.

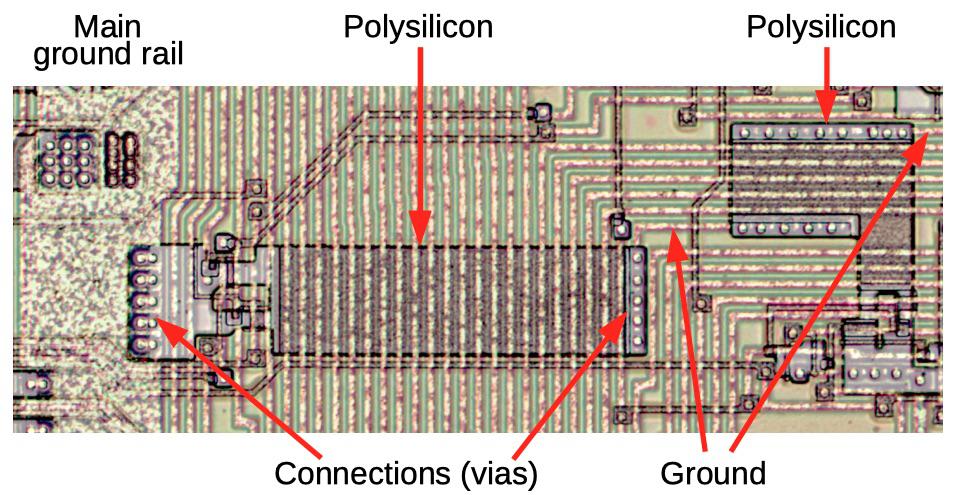

Afastando-se da fonte de energia e chegando mais perto dos pontos finais, os condutores de energia se tornam mais finos e a corrente diminui. Isso pode ser visto no condutor de energia para o endereço e os pinos de dados abaixo. À esquerda sob os contatos, o condutor com o solo é muito largo, mas vai se estreitando gradativamente, indo para a direita. Em outras palavras, à esquerda, o condutor deve conduzir corrente de todos os contatos, e do lado direito, apenas de um.

A conexão dos pinos de endereço e de dados ao terra está ficando mais fina (lado esquerdo do chip girado 90 °) A

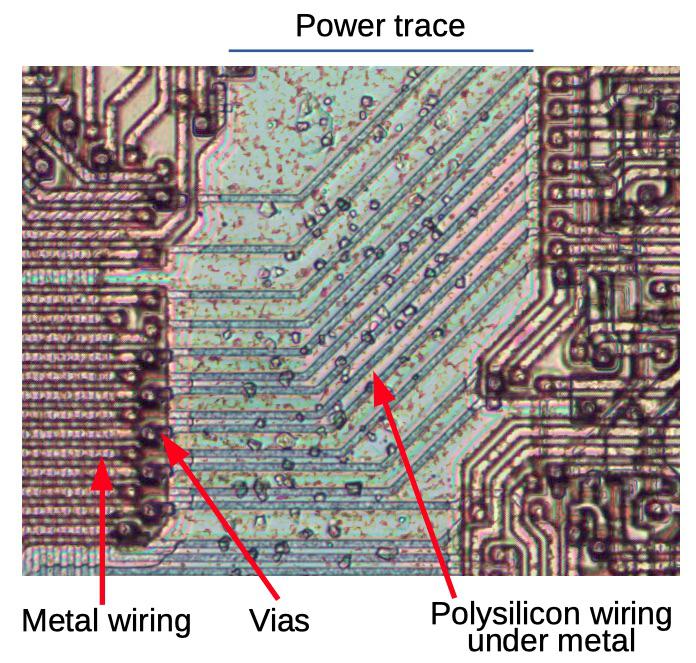

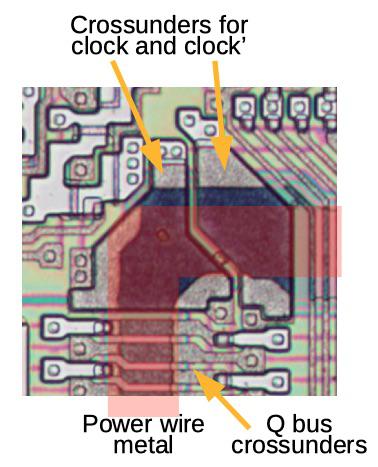

camada de metal é usada para transportar muitos sinais, não apenas energia e terra. Por causa de sua baixa impedância, é a melhor camada de transmissão de sinal. No entanto, o uso generalizado de condutores de energia e aterramento limita as capacidades da camada de metal. Para evitar o cruzamento, a maioria dos caminhos de sinal na camada de metal corre paralelamente aos caminhos de energia. Uma camada de polissilício embaixo é usada para a transmissão perpendicular do sinal. Mas o que acontece se um condutor de metal precisar cruzar uma trilha de alimentação ou aterramento? A solução é desenhá-lo de baixo [crossunder]. O sinal desce ao nível de polissilício, cruza a trilha e sobe de volta, conforme mostrado abaixo.

Essas passagens de fundo são usadas em muitos casos, não só com alimentos. No entanto, na maioria das vezes é sobre nutrição. Normalmente, os condutores metálicos são usados para transmitir sinais em uma direção e os condutores de polissilício são usados para transmitir os sinais na direção perpendicular. Em diferentes locais do chip, essas direções mudam e dependem da direção dominante da transmissão do sinal. Portanto, na maior parte, os sinais viajam sem obstáculos. E, no entanto, muitas vezes precisam pular de uma camada para outra.

Os sinais na camada de metal atravessam os caminhos de abastecimento de baixo por meio de uma camada de polissilício

Se a energia e o aterramento forem quase inteiramente direcionados à camada de metal, em alguns lugares esse circuito será interrompido e os traços que correm por baixo serão usados para fornecer energia. Isso acontece com mais freqüência nas últimas seções das pistas, onde a corrente já é baixa. Um exemplo é mostrado abaixo - onde o solo passa duas vezes a partir da parte inferior da camada de metal usando condutores de polissilício. Para reduzir a resistência, esses caminhos de desvio são feitos muito mais largos do que os caminhos de sinal e também usam silício e polissilício juntos. Pequenos círculos são feitos através de contatos [via] entre as camadas de metal e polissilício.

Foto composta mostrando caminhos de contorno de solo passando por polissilício sob os caminhos de sinal.

A camada de silício desempenha um papel menor na fiação de energia. Em particular, muitos portões são estendidos para alcançar força e aterramento do outro lado. A foto abaixo mostra os portões 8086. Observe as grandes áreas de silício dopado (branco) que são puxadas para alcançar o solo e os trilhos de alimentação. Apenas uma pequena fração do silício é usada para transistores, e todo o resto parece uma perda de espaço. No entanto, essas seções vazias de silício conectam as portas aos condutores de metal que fornecem energia e aterramento. Como o silício tem uma resistência relativamente alta, grandes áreas são usadas para isso e as próprias juntas se estendem por curtas distâncias.

Os portões feitos com silício dopado podem ser alongados para alcançar os trilhos de alimentação e aterramento. Para esta foto, a camada de metal foi removida.

Depois que o 8086 foi atualizado e fisicamente reduzido, ele teve outros problemas de fiação de energia. Com o aprimoramento da tecnologia de produção, a Intel escalou os cristais - deixou os circuitos iguais, mas os reduziu proporcionalmente. Infelizmente, reduzir o tamanho das trilhas da fonte de alimentação também reduz a corrente máxima. Para resolver esse problema, os caminhos de energia ao redor do chip foram reforçados e os circuitos internos e a fiação foram reduzidos. Isso pode ser visto na foto abaixo - por exemplo, há muito mais faixas de energia no canto inferior direito do 8086 menor.

Duas versões do 8086 na mesma escala. O cristal à direita é uma versão posterior, de tamanho reduzido.

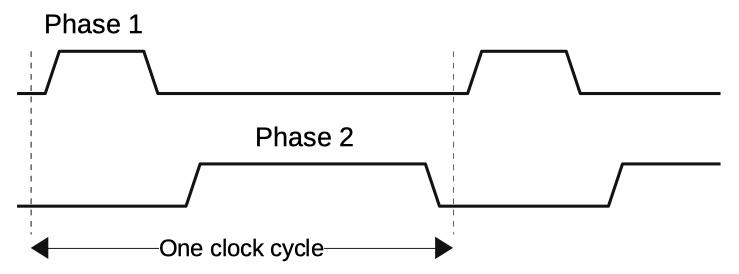

Quase todos os computadores usam sinais de clock para controlar o tempo do processador. O 8086, como muitos microprocessadores, usa um driver de clock de duas fases internamente. Um driver de clock de duas fases tem dois clocks - quando o primeiro é alto, o segundo é baixo e vice-versa, como mostrado abaixo. Alguns circuitos são ligados com o primeiro sinal de sincronização e outros com o segundo. O esquema de operação do 8086 implica que não há sobreposição entre as duas fases dos sinais de sincronização e sua assimetria - há um intervalo entre os momentos em que um sinal de sincronização torna-se baixo e o segundo aumenta.

Um driver de relógio de duas fases consiste em dois sinais de relógio de polaridade oposta

Embora quase todos os computadores usem sinais de relógio para sincronização, a máquinaA arquitetura IAS (popular na década de 1950) era assíncrona e operava sem sinais de clock. Em vez disso, cada circuito, quando concluído, envia um pulso para o próximo, disparando o próximo passo. Muitos computadores do início da década de 1950 foram baseados nesta arquitetura, incluindo CYCLONE, ILLIAC, JOHNNIAC, MANIAC, SEAC e o IBM 701. A pesquisa sobre as possibilidades da computação assíncrona continua , mas os sistemas síncronos definitivamente dominam.

Os processadores, entre outras coisas, usam sinais de clock para evitar feedback indesejado nos circuitos. Por exemplo, considere um contador de software cuja cadeia incrementa seu valor e o alimenta de volta ao contador. Você não quer que o novo valor continue aumentando.

Um método é usar gatilhos que atualizam o valor quando o sinal vai de baixo para alto. Então o contador será atualizado na única vez que for necessário. No entanto, com um sinal de sincronização bifásico, o circuito pode ser feito em travas sensíveis ao nível, cujo projeto é muito mais simples do que para triggers que são sensíveis a mudanças de sinal. Quando o primeiro sinal de sincronização é alto, a primeira metade da linha recebe um valor de entrada e executa cálculos lógicos. Quando o segundo sinal de sincronismo está alto, a segunda parte da cadeia recebe o resultado da primeira metade e executa todos os cálculos necessários, e a primeira parte é bloqueada. O ponto é que apenas metade da cadeia pode ser atualizada de cada vez, o que evita feedback indesejado.

O 8086 tem requisitos rígidos de clock de entrada, que devem ser altos durante um terço do tempo. Normalmente, o 8086 foi gerado pelo chip 8284 e um cristal de quartzo. O chip dividiu o sinal de clock de entrada por 3 para fornecer o ciclo de trabalho de clock de 33% exigido pelo 8086.

Em processadores modernos, o layout do sinal de clock é muito complexo porque o sinal deve viajar para todas as partes do chip simultaneamente. Os processadores modernos usam uma hierarquia de caminhos de relógio, equilibram os tempos de viagem ao longo de cada caminho e geralmente fornecem armazenamento em buffer separado para cada caminho. Para efeito de comparação, o layout do sinal de clock do 8086 é simples, já que sua freqüência de clock de 5-10 MHz é várias ordens de magnitude menor do que a dos processadores modernos. Nessas frequências relativamente baixas, o comprimento do caminho não importa realmente, então os pulsos do relógio do 8086 podem seguir caminhos sinuosos.

Como o 8086 usava lógica dinâmica, ele também tinha uma velocidade de clock mínima de 2 MHz. Se a frequência for menor, existe o risco de vazamento de carga antes de sua renovação, o que pode levar a falhas. A frequência mínima do clock era inconveniente do ponto de vista de depuração, uma vez que era impossível desacelerar ou parar o sinal do clock.

Sincronizar caminhos em 8086. Verde é a primeira sincronização e vermelho é a segunda, com a fase oposta

O diagrama acima mostra os caminhos do relógio do 8086. A fase 1 é verde e a fase 2 é vermelha. Na parte inferior do chip, os circuitos do driver do relógio aparecem como grandes pontos. A partir daí, os sinais de sincronização se ramificam por todo o chip. Na maior parte, as duas fases do relógio funcionam em paralelo, ao contrário da alimentação e do aterramento com seus ramos opostos.

Como os sinais de sincronização viajam para todas as partes do chip, eles exigem muito mais corrente do que os sinais convencionais e, portanto, são direcionados principalmente para a camada de metal. Quando os sinais de sincronização precisam cruzar as trilhas de alimentação, eles passam por baixo delas, conforme mostrado abaixo. Observe que as soluções alternativas de sincronização têm forma irregular - elas são muito mais do que soluções alternativas para outros sinais, como o barramento Q.

Os caminhos de desvio da fonte de alimentação são bastante grandes. O barramento Q (transmissão de comandos da fila de comandos para o decodificador) tem muito menos.

Para fornecer sinais de sincronização de alta corrente, seu circuito formador é construído em grandes transistores. A foto abaixo compara um desses transistores com um transistor lógico típico. Os transistores do driver são cerca de 300 vezes maiores, portanto, é capaz de fornecer cerca de 300 vezes a corrente. O transistor é composto de 10 transistores colocados em paralelo - 10 linhas verticais de polissilício formam 10 portas. Cada sinal de sincronização é gerado por um par de grandes transistores, um dos quais puxa para cima e o outro para baixo.

Grande transistor no driver do clock em comparação com o transistor lógico adjacente

A foto abaixo mostra o esquema do gerador de pulso de sincronização. O circuito divide o sinal de clock externo em duas fases, garante que eles não se sobreponham e os amplifica. O quadrado rosa à esquerda é uma plataforma para um driver de relógio externo. O sinal viaja por uma série de transistores que terminam nos grandes transistores do driver no lado direito. Os condutores marrons são de polissilício formando as portas. Muitos transistores têm portas em zigue-zague, portanto, um transistor grande cabe em um espaço pequeno.

Circuito de driver de relógio on-chip. A camada de metal foi removida. Transistores grandes são visíveis. Pino de entrada de sincronização externa - quadrado rosa à esquerda.

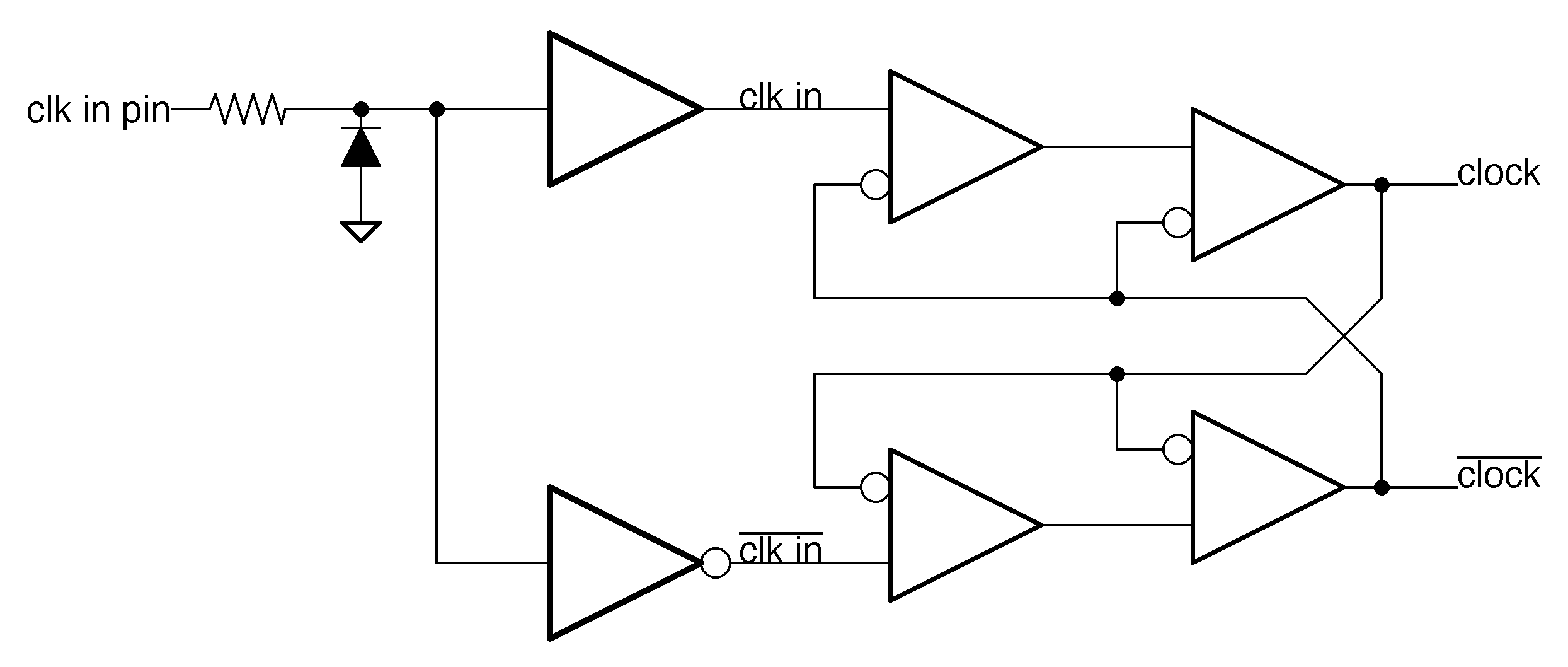

Abaixo está um diagrama esquemático ligeiramente simplificado do gerador de relógio. Os triângulos são drivers de alta corrente feitos de dois ou três transistores. A entrada inversora (círculo) puxa a saída para baixo. No lado esquerdo do pino de sincronização de entrada, há um pequeno resistor e diodo para protegê-lo (assim como os outros pinos de entrada). O sinal de sincronização é então dividido em fase invertida (parte superior) e fase invertida (parte inferior).

Diagrama esquemático simplificado do gerador de relógio 8086

Circuitos adicionais evitam que os sinais de sincronismo se sobreponham: quando um sinal está alto, isso, por meio da entrada invertida, faz com que o segundo sinal seja baixo. Para entender como isso funciona, vamos começar com o momento em que o sinal no clk in pin está alto. Os sinais clk in e clock estão altos, enquanto ^ clk in ^ e ^ clock ^ estão baixos. Agora, digamos que o sinal de entrada para clk in seja baixo, o que faz com que o sinal clk in diminua e em ^ clk in ^ suba. No entanto, a saída de ^ clock ^ não pode aumentar até que o relógio diminua. Depois disso, o sinal ^ clk in ^ passará pelos drivers inferiores, puxando ^ clock ^ para cima após dois atrasos de porta. A questão é que clock e ^ clock ^ não mudam ao mesmo tempo. Depois que um vai baixo, há um atraso antes que o outro vá alto.Como resultado, obtemos sinais de sincronização não sobrepostos.

Esta é uma descrição bem aproximada - em particular, não tenho certeza do que acontece quando um transistor puxa um sinal para cima e outro puxa o mesmo sinal para baixo. A simulação exata do processo dependerá dos tamanhos relativos dos dois transistores.

Conclusão

O 8086 usa um layout de energia interessante, mas os processadores modernos operam em um nível completamente diferente. Se o 8086 precisava de 350 mA, um processador moderno poderia precisar de mais de 100 A. O 8086 usava 3 de suas 40 pernas para alimentação e aterramento. Os processadores Intel Core i5 modernos têm 128 pinos de alimentação e 377 - aterramento (de um total de 1151 pinos). Embora as numerosas camadas de metal nos chips modernos resolvam os problemas de fiação do 8086, elas introduzem novas complicações, como dividir o chip em seções de alimentação, que permite desligar as seções não utilizadas.

Em processadores modernos com suas velocidades multi-gigahertz, a fiação dos sinais de sincronização é muito mais complicada, porque um milímetro extra de trilha pode afetar negativamente o sinal de sincronização. Para resolver esses problemas, os processadores modernos usam coisas como H-trees ou redes de distribuição de clock, em vez de apenas trilhas ramificadas como o 8086. Enquanto o 8086 tinha um circuito simples de geração de clock de duas fases, os processadores modernos costumam usar loop de bloqueio de fase para sintetizar o sinal de clock. e muitos circuitos espalhados por todo o chip que fornecem e controlam sinais de clock. Mas embora o 8086 seja muito mais simples do que os processadores modernos, ele contém muitos exemplos de circuitos interessantes.