Você quer saber como conseguir um emprego projetando eletrônicos para espaçonaves? Recentemente, recebi uma oferta para uma entrevista para o cargo de designer FPGA da Blue Origin (veja acima). Pessoalmente, não preciso dessa posição (já tenho uma posição de designer ASIC em outra empresa), mas observei que os requisitos técnicos para candidatos na Blue Origin coincidem exatamente com o conteúdo do seminário para alunos e alunos do terceiro ano, que será realizado de 15 a 17 de setembro na exposição ChipEXPO em Skolkovo , com o apoio da RUSNANO. Embora, é claro, no seminário tocaremos nas tecnologias Verilog e FPGA apenas no nível inicial: conceitos básicos e exemplos simples, mas já interessantes. Para conseguir um emprego depois disso na Blue Origin, você ainda precisa de alguns anos de estudo e trabalho.

Devido ao coronavírus, o seminário será remoto, de forma que não só crianças em idade escolar e estudantes de Moscou, mas também toda a Rússia, Ucrânia, Cazaquistão, Califórnia e outros países e regiões poderão participar. Professores e engenheiros do MIET, HSE MIEM, MIPT, Chernihiv Polytechnic University, Samara University, IVA Technologies e fpga-systems.ru conduzirão fisicamente as palestras e auxiliarão remotamente os participantes .

Para participar primeiro, antes mesmo do seminário, você precisa concluir três partes de um curso teórico da RUSNANO, sob o título geral "Como funcionam os criadores de nanochips inteligentes": "Do transistor ao microcircuito", "Lado lógico do circuito digital", "Lado físico dos circuitos digitais". Este curso é essencial para que você entenda o que está fazendo durante o workshop. Ao receber o certificado de conclusão do curso teórico online, você pode ir ao escritório da RUSNANO em Moscou e receber uma taxa gratuita para um seminário prático (se ficarem, os alunos têm prioridade). Com esta placa você pode trabalhar em casa, antes, durante e depois do seminário Skolkovo.

Como receber o pagamento, se preparar para o seminário e o que ele incluirá:

As instruções sobre como obter uma taxa estão no site STEMford . STEMford é um programa educacional para alunos da eNano , uma subsidiária da Fundação RUSNANO para Programas Educacionais de Infraestrutura. Aqui está seu escritório para visitar:

Antes do laboratório, você precisará ter o Intel Quartus Prime Lite Edition instalado em seu computador. As instruções sobre como fazer isso estão no fragmento gratuito do livro "Digital Synthesis: A Practical Course" editado por A. Yu. Romanov, Yu. V. Panchul. DMK Press, 2020.

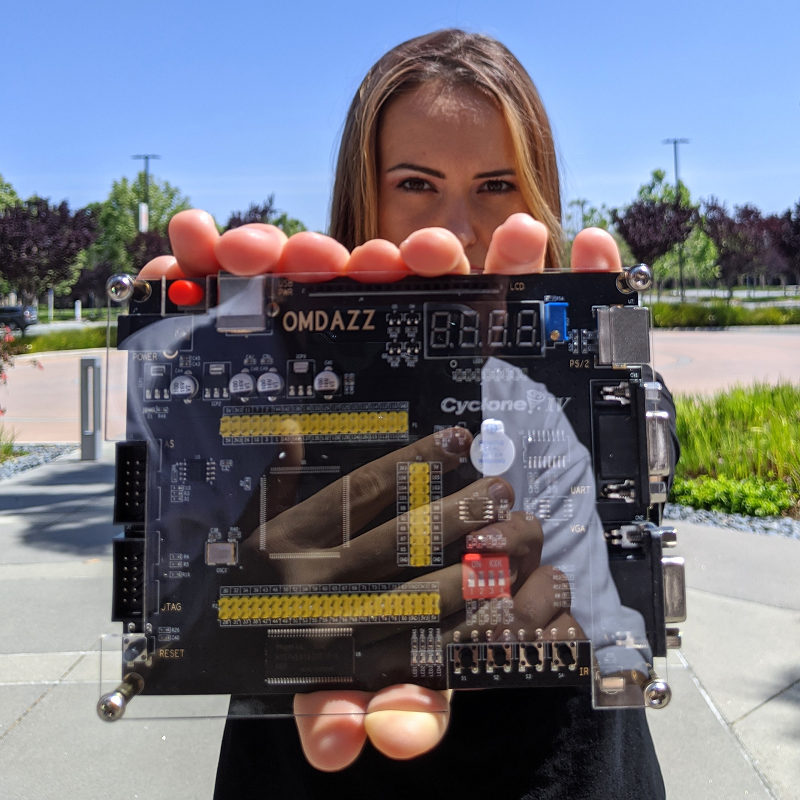

Em geral, Digital Synthesis é um livro útil para um seminário, ele descreve exercícios que serão apresentados com algumas variações no seminário, embora por exemplo, em vez do processador educacional schoolMIPS, um mais modernoschoolRISCV : No final do livro Digital Synthesis , há uma entrevista bastante divertida com um casal de recém-casados Vladislav e Elena Sharshin, que, junto com seu colega Andrey Papushin, a Intel trouxe para a Califórnia para uma vitória de prata na competição InnovateFPGA: Aqui está uma das pranchas que serão usadas no seminário. Se não houver pranchas suficientes para você, ou se você não for aluno, pode solicitar uma prancha no AliExpress e em outros locais: 1 , 2 , 3 , 4 : O que vai acontecer no seminário? Aqui estão as partes do programa :

15 . .

: , « » ().

15.00. , .

15.15-15.30. -: Apple iPhone: .

, . , .

15.30-16.00. : Verilog. /FPGA Intel Quartus Prime Lite Edition. .

16.00-16.30.

///-, , c .

16.30-17.00. .

17.00-17.30. : , .

17.30-18.00. .

18.00-19.00. ZEOWAA OMDAZZ Intel FPGA Cyclone IV: : ( ). Terasic DE10-Lite Intel FPGA MAX10: : ( ).

19.00-21.00. , : , , ,

.

O primeiro dia é baseado na experiência da realização do seminário do ano passado em Moscou, descrita em um artigo sobre Habré : O

segundo dia é baseado na experiência da realização de uma escola de verão em Zelenogrado no ano passado e seminários em Samara:

16 . .

: , , , .

15.00-15.15. -: : , .

.

15.15-15.30. : VGA.

.

15.30-16.00. .

16.00-16.30. . Digilent Basys3 Xilinx FPGA Artix-7. .

, fpga-systems.ru.

16.30-17.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

17.00-17.30. : Linear Feedback Shift Registers (LFSR) . Verilog VHDL LFSR . LFSR VGA .

, .

17.30-18.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

18.00-19.00. .

.

18.00-21.00. , . .

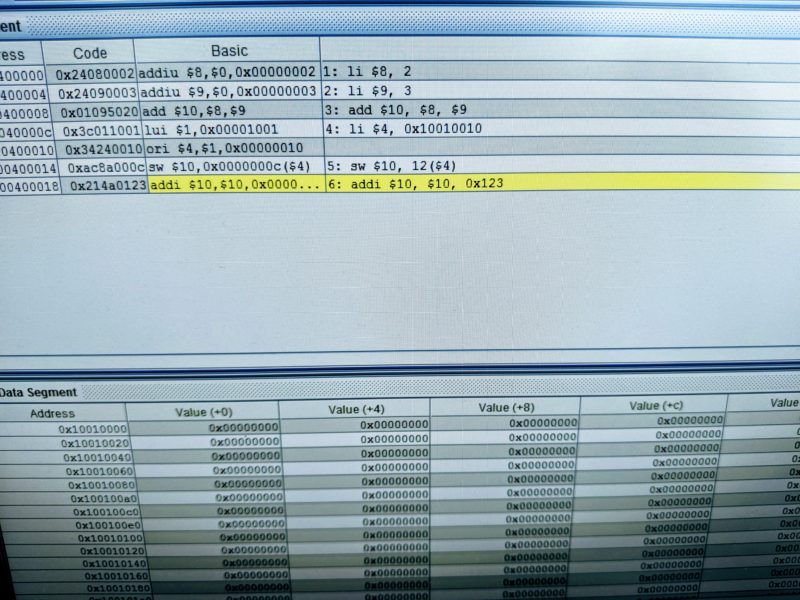

O terceiro dia será baseado na experiência do programa educacional em processadores de Stanislav Zhelnio e Alexander Romanov . Só antes eles desenvolveram e usaram o processador de aprendizagem schoolMIPS, e agora vamos usar o schoolRISCV. A arquitetura RISC-V é muito semelhante a MIPS e outras arquiteturas RISC (SPARC, ARM, POWER, etc.), mas limpa de suas muletas, o que fazia sentido em processadores simples, mas interfere em processadores complexos (janelas de registro em SPARC, que não fazem sentido em software com uma grande pilha; slots de atraso de ramificação no MIPS até Rev6, que são bons em um pipeline estático simples com busca sequencial de instruções, mas se transformam em uma dor de cabeça em um pipeline dinâmico, etc.).

Uma vez que existem pelo menos três empresas na Rússia que projetam processadores na arquitetura RISC-V, este é um bom candidato para o futuro processador russo de ponta embutido e talvez até mesmo para desktop e servidor, e já que o RISC-V substitui com segurança o MIPS como um processador funcional cavalos para experimentação arquitetônica e microarquitetura em universidades mundiais, então é melhor para os alunos ensiná-los.

17 . .

— , ..., . .. (), « » ( ).

15.00-15.15. -: ENIAC , IBM/360 Cray-1 Intel, ARM RISC-V: , .

.

15.15-16.30. : . RISC-V .

, - .

16.30-17.30. : . schoolRISCV, . .

, IVA Technologies.

17.30-17.30. . .

.

17.30-18.00. Aula de conclusão: Próximas etapas no domínio do projeto de circuitos digitais e aplicação desse conhecimento para projetar sistemas embarcados e aceleradores de computação de inteligência artificial

Alexander Yurievich Romanov.

18,00-21,00. Exercícios adicionais e projetos individuais para os alunos trocarem o processador e integrá-lo a dispositivos periféricos. Com ajuda de alunos de graduação e pós-graduação em microeletrônica das universidades participantes.

Aqui está Stanislav Zhelnio ensinando crianças em idade escolar no verão passado em Zelenograd: Nos

vemos em um seminário na ChipEXPO virtual em Skolkovo! Tentaremos realizar uma parte do evento lá e ao vivo, com a ajuda dos professores do MIET, HSE MIEM e MIPT, mas se o vírus não permitir, faremos de forma distribuída.