O artigo foi elaborado com base na minha própria experiência de tentativas de explicar este tema para mim, estagiários e colegas curiosos de forma a não mergulhar na abstrusa selva acadêmica, mas da forma mais simples e transparente possível, na linguagem cotidiana. Aprendi a trabalhar com FPGAs sem estudar e treinar neste tópico, e sei por experiência própria como é difícil entender algo sem uma base teórica neste tópico e nos circuitos. Para um criador experiente, o acima exposto é elementar. Mas para algum aluno do quarto ano, o artigo será útil e ajudará a entender todas essas calças, montagens e agarres.

No artigo, usarei termos com a duplicação de sua versão em inglês entre colchetes. Isso é feito porque uma terminologia unificada não é estabelecida e, com a duplicação, é mais fácil entender qual conceito está sendo discutido e, se necessário, encontrar informações sobre ele em fontes em inglês.

Introdução

Darei uma breve introdução na linguagem dos conceitos simples.

Para que algo funcione no FPGA, você precisa carregar (fazer upload, costurar) o arquivo do firmware nele, usando o programador e o utilitário de firmware. O arquivo de firmware é o produto de uma compilação CAD de um certo projeto - pastas com arquivos, cada uma das quais descreve algum aspecto do projeto. Em casos simples, o próprio usuário descreve apenas arquivos com código-fonte, um arquivo com pinagem e um arquivo com restrição de tempo. O resto dos arquivos são controlados silenciosamente pelo CAD. Dessa tríade, apenas o arquivo de restrição de tempo é formalmente opcional.parte do projeto. Na verdade, se o seu projeto não contém frequências superiores a 30-50 MHz, é provável que funcione de alguma forma sem esse arquivo. Esta opção é apropriada para a facilidade de criação dos primeiros projetos educacionais. No entanto, se o seu projeto de treinamento já contiver altas frequências de clock e não estiver equipado com um arquivo de restrição de tempo, o processamento de dados provavelmente será interrompido em algum lugar dentro do FPGA e você não será capaz de descobrir em que ponto do projeto. Quanto ao trabalho, não ao estudo, a descrição de todo o arquivo de restrições é estritamente necessária . É sua responsabilidade verificar e validar a funcionalidade do seu projeto.

O compilador coloca seu projeto no chip FPGA, recebe um arquivo de conexões de todos os elementos físicos. O analisador de tempo usa o arquivo de conexão para calcular todas as durações das transferências de dados para o FPGA. Essas durações não devem ser infinitamente longas ou muito curtas. O arquivo de restrições de tempo informa ao analisador em que quadro essas durações devem estar. Usando os resultados da análise de tempo, o desenvolvedor pode ver em quais partes do projeto há uma margem no tempo e, portanto, na frequência, e onde essa margem não existe.

Os sistemas síncronos sincronizam o trabalho de processamento de dados usando sinais de relógio de sincronização, que no jargão são chamados de relógios do relógio inglês... Os resultados intermediários das operações são armazenados em registradores capazes de memorizar o estado na entrada no momento da chegada da transição do sinal do clock e mantê-lo na saída até o próximo ciclo do clock.

Assim, os circuitos síncronos consistem em transferências de dados entre registros ( RTL, lógica de transferência de registro, transferência r2r ). E um aspecto chave da análise temporal consiste em medir a folga ( folga ). Esta palavra se traduz literalmente como "reserva de tempo", "flacidez", mas no ambiente de língua russa, papel vegetal do inglês é freqüentemente usado - "folga". Em interregister transferências, estamos a falar de pré- calças ( Setup ) e segurar calças ( Reter ).

Transferência entre registros

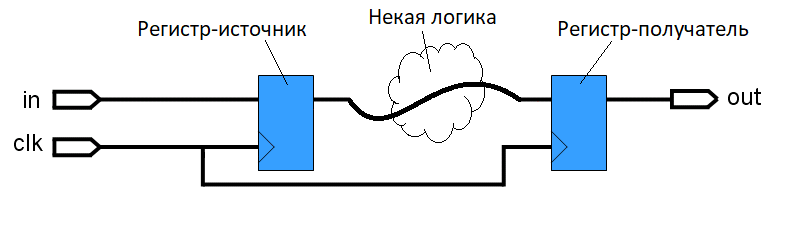

A transferência entre registros (Fig. 1) é considerada como um sistema de dois registros conectados sequencialmente que operam em relógios síncronos no caso geral. No caso simples, em um fragmento. Um registro desempenha o papel de fonte (fonte) e o outro papel de receptor de dados (destino). E na próxima transferência entre registros, este registro de destinatário já será considerado como a fonte, etc. Entre os registradores no caminho de dados está alguma lógica combinacional arbitrária definida pelo usuário. É assíncrono, pois não possui elementos de memória com sinal de sincronização, como registradores. Essa lógica é aquele comportamento, aquelas operações lógicas que o usuário descreve com seu código. Registros são aquelas "variáveis" de um bit que o usuário dá nomes no código e opera separadamente,ou combinando em vetores e matrizes.

Figura: 1. Esquema de transferência de dados de registro para registro

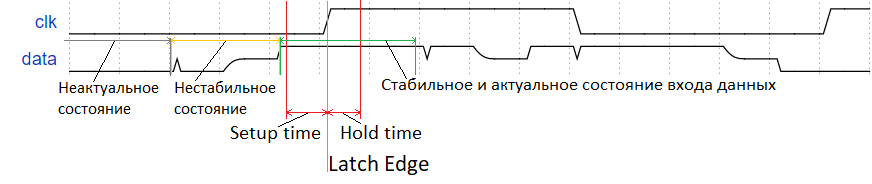

Existem dois conceitos associados ao recebimento de dados pelo registro de recebimento: Tempo de configuração e Tempo de espera. Eles delineiam o intervalo de tempo durante o qual o sinal na entrada do receptor deve ser estável e relevante. Estável - significa essencialmente que sua tensão deve estar muito próxima de um dos dois estados lógicos - "0" ou "1", e não oscilando entre eles com risco de confusão. Relevante - significa que este bit de informação deve, em seu significado, estar relacionado a esta batida do relógio que irá capturá-lo, e não um bit atrasado da batida anterior.

Tempo de configuração - tempo predefinido, o tempo mínimo durante o qual antes da chegada do relógio o sinal de dados já deve estar definido para um estado estável.

Hold time - o hold time, o tempo mínimo que após a chegada da frente do relógio, o sinal de dados ainda deve ser mantido em um estado estável.

Ou seja, os dados na entrada do receptor devem estar estáveis e atualizados não apenas no momento da chegada da frente do relógio, mas também durante um certo intervalo de tempo de proteção em torno dele (Fig. 2), com uma duração de pelo menos Setup_time + Hold_time. Se a condição de estabilidade dos dados for satisfeita durante este intervalo, o registro será definitivamente capaz de capturar os dados de entrada sem erros, caso contrário, ninguém garante que não haverá falha.

Figura: 2. Tempo de configuração e tempo de espera como um intervalo de guarda em torno da borda de captura na entrada do relógio do registrador

Os valores de Setup time e Hold time são estritamente definidos pelo fabricante do FPGA. Elas dependem da tecnologia de produção do cristal e são consideradas constantes para análise, as mesmas para cada registro no cristal. Em todo caso, esses valores não dependem de forma alguma do usuário, sua contabilização é uma tarefa apenas para a utilidade da análise do tempo. Não é importante para nós saber a que eles são iguais, é importante para nós apenas saber que eles existem e não são iguais a zero.

A essência da análise de tempo é calcular as folgas no tempo para cada par de registros do projeto, entre os quais há transferência de dados, que os dados têm que ficar estáveis durante o intervalo de guarda. Existem muitos pares r2r no projeto, milhares ou até milhões, mas cada um deles deve ser analisado para garantir que o projeto funcione.

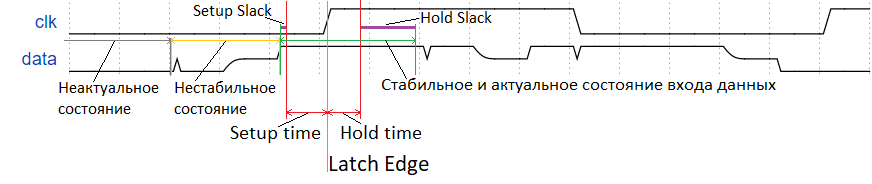

Existem também duas folgas, respectivamente - Setup Slack e Hold Slack (Fig. 3).

Setup Slack caracteriza a margem de tempo que os dados possuem desde o momento de estabilização até o início do intervalo de tempo de Setup.

Hold Slack caracteriza a margem de tempo que os dados têm desde o final do intervalo de tempo Hold até a perda de estabilidade dos dados.

A calça deve ser positiva. Se a folga for negativa, a condição de estabilidade dos dados de entrada não foi atendida e os dados baterão. Quanto mais folga - melhor, mas você precisa entender que em cada destino de registro, suas folgas predefinidas e de retenção têm um tempo comum para dois. Isso significa que um aumento em uma folga sempre leva a uma diminuição na outra. Portanto, a melhor opção é quando ambas as calças são positivas e aproximadamente iguais entre si, ou seja, o equilíbrio das calças é observado.

Figura: 3. Folgas positivas, a condição para recepção de dados bem-sucedida é atendida, mas não há equilíbrio entre as folgas

Cálculo de folga

Agora vamos ver como essas folgas são calculadas. Vamos começar com o Setup Slack.

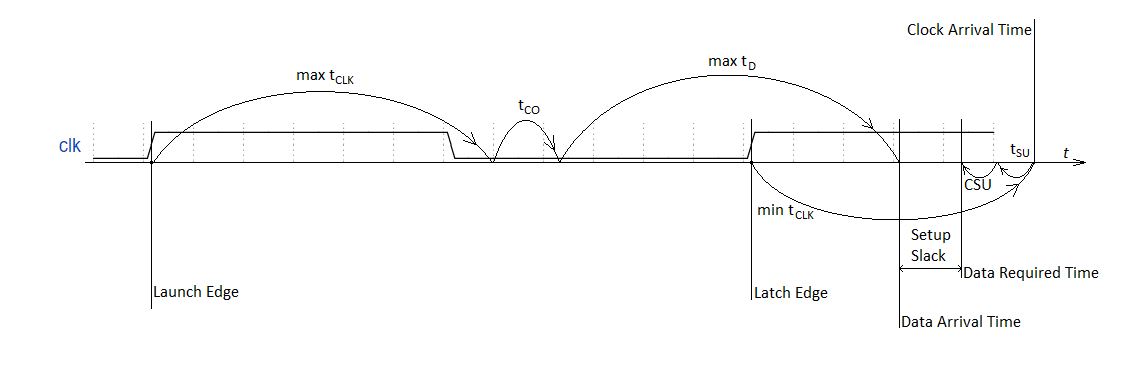

Considere o esquema de transferência de dados na Fig. 4.

Fig. 4. Esquema de transferência de dados

Aqui, introduzimos conceitos como frente de disparo, frente de captura, tempo de chegada de dados, tempo de espera de dados e tempo de chegada do relógio.

O Launch Edge é a frente do relógio que veio para a entrada do registrador de origem e iniciou o processo de transferência de dados.

O Latch Edge é a frente do relógio que chega ao registrador de recepção e o força a capturar os dados na entrada.

O momento de chegada dos dados ( Data Arrival Time ) é definido como a chegada real dos dados no registro receptor.

O Data Required Time é definido como o tempo que leva para os dados chegarem ao destino antes do tempo predefinido no registro de destino.

O tempo de chegada de um relógio ( Clock Arrival Time ) é definido como o tempo de passagem da borda da captura desde a entrada do relógio de todo o circuito até a entrada do relógio do receptor. Além disso, a frente de captura significa a próxima frente após a frente de lançamento. A frente de lançamento permite que os dados da fonte para o destinatário e, após um período de relógio, a frente de captura captura esses dados no lado do destinatário.

A entrada do relógio de todo o circuito é entendida como um único ponto de onde o relógio diverge para todos os registros que operam nele. Normalmente, é a saída do buffer de relógio global ou a saída do PLL. No caso mais primitivo, é a perna do FPGA, à qual o gerador de clock está conectado.

Os termos envolvidos na análise temporal podem não ter um valor de ponto, mas uma certa faixa de valores possíveis, dependendo do traço do projeto e da temperatura do cristal. Portanto, a pior folga é analisada. Uma troca de dados é considerada bem-sucedida se, mesmo nas piores condições para uma folga, ela permanecer positiva.

Como o momento de chegada dos dados se relaciona com a borda de disparo?

Consideramos a chegada de dados como passando por uma cadeia com um registro de algum evento iniciado por uma borda de disparo.

A borda inicial aparece na entrada do relógio do sistema, em seguida, atinge a entrada do registro de origem por algum tempo, então por algum tempo esse registro é acionado e envia novos dados para a saída, então esses dados passam pelos circuitos lógicos combinacionais para o registro receptor. A variante pior e mais lenta da passagem de dados é considerada, portanto, os termos vêm com o prefixo "máximo".

Nesta fórmula, o termo para a borda de disparo carrega o significado do ponto de referência em relação ao qual os eventos se desenvolvem, e não algum valor medido em nanossegundos.

PrazoÉ o tempo máximo que leva para a borda de disparo ir da entrada do relógio de todo o circuito até a entrada do relógio da fonte. Como regra, o analisador simplesmente pega o intervalo de tempo de “exatamente não menos que” a “exatamente não mais que” e substitui o limite superior “definitivamente não mais que” nesta fórmula. Este valor é independente do usuário. O compilador decide por si mesmo onde colocar o registro no cristal e leva em consideração o tempo que leva para o relógio chegar até ele. A rede de conexões por meio da qual o sinal do relógio diverge do buffer do relógio global para os registradores é projetada de modo que o sinal do relógio alcance qualquer registrador quase no mesmo período de tempo. Portanto, na verdade, a diferença entre e extremamente pequeno, mas ainda assim levado em consideração.

Prazo- este é o tempo do relógio para a saída , que o registrador gasta para ver a transição na entrada do relógio alterar os dados em sua saída. O analisador considera este valor igual para todos os registros no chip. Este valor é independente do usuário.

O último termoÉ o tempo máximo para um evento (dados) passar pela lógica de combinação entre registros, que é definida pelo usuário. Este valor é altamente dependente do usuário. Ele expressa a quantidade de lógica combinatória entre os registradores. Por sua vez, longas cadeias de lógica combinatória são freqüentemente o resultado de uma codificação imprecisa pelo usuário.

No momento em que o fragmento chega ao destinatário é mais fácil de calcular:

Este é o primeiro momento em que a borda de captura atinge a entrada de clock do registrador de recepção.

Prazo- este é o tempo mínimo em que a frente de captura atingirá a entrada do relógio do destinatário, ou seja, por analogia com a fórmula anterior, este tempo é “definitivamente não menor que”. O traço, neste caso, significa que estamos falando sobre a entrada do relógio do destinatário, não a fonte.

O tempo de espera pelos dados é definido como o tempo que leva para os dados chegarem ao receptor antes do tempo predefinido no registro do receptor:

Prazo - esse tempo de configuração já é conhecido por nós, que é considerado igual para cada registro no cristal. Este tempo é independente do usuário.

PrazoÉ a incerteza de configuração do relógio , incerteza de tempo predefinido. Como qualquer outra incerteza na análise temporal de um CSU não é um processo físico, mas uma forma de refletir a influência do jitter na análise, ou simplesmente uma forma de introduzir um tempo de guarda na análise apenas no caso. Em palavras simples, é uma reserva de tempo para levar em conta processos difíceis.

Agora que esses termos estão definidos, podemos definir uma folga predefinida como a menor diferença entre o tempo que é permitido viajar até o destino e o tempo que realmente leva.

Agora, vamos expandir esses termos e reorganizá-los um pouco:

Novos termos apareceram aqui.

É claro sobre o período, este é o período da frequência do relógio, ou seja, tempo entre Launch Edge e Latch Edge.

Prazo- este é o clock skew - o valor mínimo da propagação do tempo de chegada de um relógio da entrada do relógio do sistema para diferentes registradores síncronos. O spread mínimo do clock é definido como a diferença entre o menor atraso do clock para o destinatário e o maior atraso do clock para a fonte.... O analisador não faz diferença ao estimar esse tempo para diferentes registros em um chip.

É assim que calculamos a folga predefinida. Uma margem positiva é boa, uma margem negativa é ruim. Slack se traduz literalmente em flacidez. Portanto, se houver uma folga, a transferência entre registros não está configurada "vnatyag", a "thread" condicional cede livremente. A folga é negativa - significa que a linha de transmissão foi puxada e quebrada.

A Figura 5 mostra como a fórmula de folga pode ser representada graficamente:

Fig. 5. Representação gráfica da expressão de folga de configuração

Mostra a relação no fundo do sinal do relógio, e este é o sinal do relógio na entrada do relógio do sistema, e não na entrada de nenhum dos registradores.

Agora vamos calcular a folga de retenção de maneira semelhante .

Também pode ser representado por uma expressão em que os termos mudaram de sinal:

Esses termos são agora considerados do outro lado.

Agora, a variante mais rápida de passagem de dados é considerada aqui e onde "max" era "min".

O momento de chegada da frente do clok também é visto de uma maneira diferente, o mais tardia possível:

É importante observar que, no caso do Hold Slack, as frentes Launch Edge e Latch Edge agora são a mesma frente, em vez de duas frentes diferentes separadas pelo período do relógio. Nessa situação, o registro do destinatário precisa ter tempo para reter os dados na entrada durante o tempo de retenção a partir da chegada do relógio. Mas os dados são alterados em sua entrada pela mesma frente, que veio de outro lugar para o registrador de origem. Portanto, na análise da folga de retenção, a diferença éé zero, não ponto.

O tempo necessário, neste caso, é definido como o tempo durante o qual os dados não devem mudar na entrada dos dados do destinatário, de modo a não capturar o tempo de espera:

Prazo - isso já é conhecido por nós Hold time, o tempo de espera. É considerado igual para todos os cadastros do chip e não depende do usuário.

PrazoÉ a incerteza do tempo de espera , a incerteza do tempo de espera. Em geral, tem o mesmo significado que CSU e, via de regra, é considerado igual a ele.

Se, como no caso da folga predefinida, você expandir os termos e trocá-los, a expressão da folga de retenção pode ser transformada na seguinte forma:

Outra olhada nesta fórmula

Acima, foi apresentado um método de cálculo de folgas, característico da compreensão humana dos processos em curso. Aqui "a frente está chegando ...", "os dados estão chegando ...". Se você estiver interessado, como um suplemento, direi como o analisador de restrições de tempo imagina esses cálculos.

O analisador agrupa os termos de maneira diferente, com base nos motivos da máquina. Mas, no final, o resultado é o mesmo.

Ele usa os termos Relação de configuração de relógio ( SR ) e Relação de retenção de relógio ( HR ) - que podem ser traduzidos como a proporção do tempo entre as bordas de disparo para predefinição e retenção, respectivamente.

A Figura 6 mostra como essas frentes estão relacionadas:

Fig. 6. Frentes usadas em cálculos de folga.

Você pode converter imediatamente as expressões resultantes em uma forma mais compreensível:

O mais longo tempo entre registros (Maior r2r necessário) é o tempo máximo disponível para os dados chegarem ao destino antes do início do intervalo predefinido:

O mais longo atraso entre registros (mais longo r2r Delay) é o tempo que leva para transferir dados do registro de origem para o registro de destino ao longo do caminho mais longo:

Agora podemos definir a folga predefinida como a diferença entre o tempo disponível para chegar ao registrador de destino e o tempo real para chegar lá:

Expandir os termos desta fórmula nos dará a representação familiar da folga predefinida:

Agora sobre a folga de retenção. O menor requisito r2r é o tempo que leva para manter os dados na entrada do registro de destino:

Menor atraso entre registros:

Agora definimos a folga da predefinição como a diferença entre o tempo mais rápido para os dados saírem da entrada do receptor e o tempo que leva para mantê-los lá:

Ao expandir os termos, a expressão também assume a forma já familiar:

Que conclusões podem ser tiradas de fórmulas enfadonhas?

Vimos como as folgas são calculadas. Como usar esse conhecimento?

Vejamos as expressões de folga novamente:

Se algumas folgas do projeto se tornarem negativas, podemos alterá-las alterando seus termos. Ou seja, vemos como podemos consertar calças ruins.

Vemos termos que não dependem do usuário, mas dependem apenas da tecnologia de cristal. isto... Não há como interferir.

Vemos os termos CSU e CHU, que o analisador geralmente toma igual ao parâmetro CU - Incerteza do relógio, a instabilidade da frequência do relógio. De modo geral, esse parâmetro é pequeno, dezenas de picossegundos. Ele é especificado pelo usuário no arquivo de restrições. E o usuário, por sua vez, tira isso da especificação do gerador de relógio. Considera-se que um clock buffer ou FPGA PLL interno, que recebe um clock externo do oscilador e o converte em clock interno na entrada do clock do sistema, mantém o valor de CU igual ao recebido do oscilador. Se CU não for especificado, o analisador irá configurá-lo para algum valor padrão, por exemplo, Quartus o configurará para 20 ps. No caso geral, este termo nos diz que é melhor usar osciladores altamente estáveis com uma pequena quantidade de instabilidade para clocking. Bons osciladores são da ordem de 20-60 ps.

O termo do período mostra que a maneira óbvia de combater o mau direcionamento da transmissão de dados é reduzir a frequência do clock. É razoável, mas nem sempre aceitável, uma vez que os termos de referência geralmente requerem algum desempenho do sistema, abaixo do qual você não pode ir. E o desempenho depende diretamente da velocidade do clock. Também podemos ver a diferença entre a folga predefinida e a folga - a folga é independente da frequência.

E finalmente, o termoessencialmente caracteriza a eficiência do código escrito. Portanto, a principal maneira de resolver os problemas de folga é reescrevê-lo corretamente. Grande momentoaparece em projetos de hardware muito complexos que exigem muita lógica combinacional. Se você tiver essas construções complexas em seu projeto, a maneira clássica de resolver o problema é dividir uma transferência r2r complexa em várias outras simples, inserindo mais 1-2 registradores na sequência de operações. Neste caso, o atraso nos ciclos para a operação aumentará, mas a velocidade da operação aumentará. Por exemplo, adicionar vários vetores em um ciclo de clock não é uma boa ideia. É melhor adicionar vários vetores um a um, com somas intermediárias. Pode ser impossível quebrar algumas construções complexas em um pipeline de várias outras simples - então, tal lógica precisa ser reescrita de alguma forma fundamentalmente diferente.

Conclusão

O objetivo deste artigo é aprender sobre a existência do conceito de folga e de que depende fisicamente essa folga. Sabendo disso, você pode estudar de forma independente os relatórios do analisador de restrições de tempo, tirar conclusões e depurar o desempenho do seu projeto. Estas são fórmulas pelas quais dificilmente você terá que fazer um cálculo real. Você nem precisa se lembrar deles de cor. É importante apenas entender a lógica do que está acontecendo na transferência entre registros e entender quais fatores determinam a velocidade do projeto.