A IBM anunciou o desenvolvimento de uma tecnologia de processo de 2 nm.

O que foi anunciado:

- 2 nm.

- 50 bilhões de transistores em uma área do tamanho de um prego. Mais tarde, eles esclareceram - em uma área de 150 m2 - ou seja, 333 milhões de transistores por milímetro quadrado (

- MTx / mm 2 ).

- O passo da porta do transistor (Contacted Poly Pitch, CPP) é de 44 nm, o comprimento da porta é de 12 nm.

- (Gate All Around, GAA). – , IBM (horizontal nanosheets, HNS).

- HNS .

- 45% 75% 7 .

- (EUV) HNS 15 70 . , SRAM.

- 5 .

Esta é realmente uma tecnologia de processo de 2 nm? Hoje a TSMC é líder na produção de chips. Traçamos a relação entre os nomes dos processos TSMC e a densidade do transistor aproximando a curva com um coeficiente de determinação de 0,99.

De 28 nm a 5 nm, os números reais são usados de acordo com IC Knowledge e TechInsights. Os números de 3nm são baseados em comunicados de imprensa da TSMC. 2 nm e 1,5 nm é a nossa extrapolação.

Usando o gráfico, você pode converter a densidade dos transistores em uma tecnologia de processo TSMC equivalente (TSMC Equivalent Node ou TEN). Obtemos 2,9 nm para 333 MTx / mm 2 . Do nosso ponto de vista, verifica-se que se trata de uma tecnologia de processo de 3 nm, não de 2 nm.

Para comparar com mais detalhes o anúncio da IBM com os anúncios anteriores da tecnologia de processo 3nm e do processo 2nm proposto, várias suposições precisam ser feitas.

- É conhecido pelo anúncio que o CPP é de 44 nm.

- Suponha que a produção esteja usando a tecnologia de colocação de transistor mais rígida, Single Diffusion Break (SDB).

- Com base na foto em corte do anúncio, a tecnologia Buried Power Rails (BPR) não é usada. O BPR é necessário para reduzir o tamanho da trilha HNS para 5,0 - então, vamos supor que esse valor seja 6,0 neste processo.

- Para atingir uma densidade de 333 MTx / mm 2 , o Mínimo Metal Pitch teria que ser 18 nm - um valor muito agressivo que provavelmente exigiria fotolitografia multi-matriz EUV.

2nm IBM versus tecnologia de processo 3nm existente

A tabela a seguir compara os designs da IBM com nossas estimativas de processo de 3 nm da Samsung e TSMC. Sabemos que a Samsung está trabalhando com HNS também, e a TSMC optou por FinFET 3nm. Samsung e TSMC também anunciaram um aumento de 3 nm na densidade do transistor para sua tecnologia de processo em comparação com 5 nm. Portanto, a densidade dos transistores das três empresas é conhecida por nós e podemos calcular o TEN para todas. O TEN da IBM é 2,9; pode-se ver que a Samsung tem 4.7 e a TSMC tem 3.0. Novamente, verifica-se que 2 nm da IBM é mais semelhante a 3 nm da TSMC, enquanto a Samsung está ficando para trás.

Os parâmetros indicativos necessários para atingir as densidades anunciadas são destacados em vermelho, assumindo que todas as empresas estão usando a tecnologia SDB. A altura das pistas é a menor no TSMC, pois sem o BPR no FinFET este parâmetro pode chegar a 5,0, porém, para que o HNS tenha a mesma altura, deve-se utilizar o BPR.

2nm IBM versus tecnologia de processo 2nm existente

Na tabela a seguir, estimamos os valores dos parâmetros para a tecnologia de processo de 2 nm da Samsung e TSMC. Em nossa extrapolação, presumimos que as empresas estão usando o BPR (a tecnologia BPR ainda não está madura, mas provavelmente entrará em operação quando anunciarem um processo de 2 nm em 2023-2024). Vamos supor também que as empresas adotem a arquitetura do forksheet NHS (HNS FS) para atingir uma altura de pista de 4,33. As estimativas de CPP e MPP são baseadas nas tendências atuais de miniaturização de tecnologia.

Consumo de energia e desempenho

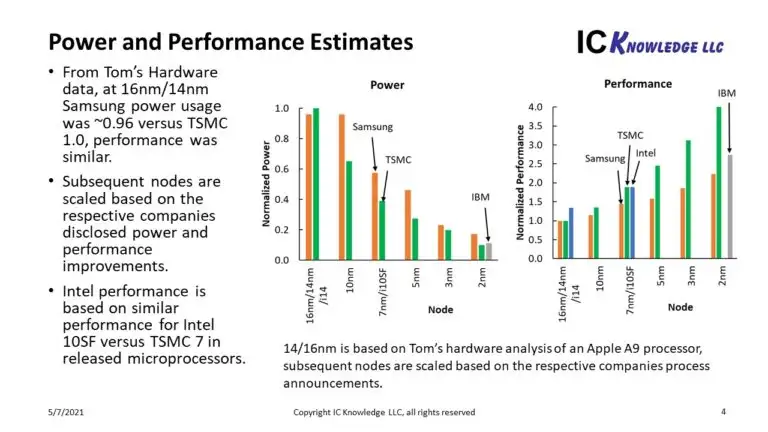

Este ano já fiz suposições sobre o consumo de energia e o desempenho de dispositivos Samsung e TSMC usando dados de desempenho adicionais da Intel. A extrapolação é baseada em garantias de empresas e em comparações do mundo real entre processos de 14 nm e 16 nm.

Como a IBM comparou as melhorias no consumo de energia e desempenho com processos de fabricação avançados de 7 nm, posso traçar seus dados nos mesmos gráficos.

Com o uso do HNS, a IBM obteve economia de energia significativa, tornando seu processo de 2 nm mais eficiente do que o processo de 3 nm da Samsung e TSMC. Embora, em nossa opinião, quando o TSMC muda para HNS em 2 nm, seu consumo de energia não será inferior ao da IBM. Em termos de desempenho, assumimos que o processo de 3nm da TSMC ultrapassará o processo de 2nm da IBM.

Claro, todas essas são apenas estimativas baseadas em um grande número de suposições.

Conclusão

Depois de analisar o anúncio da IBM, chegamos à conclusão de que sua tecnologia de processo de 2 nm é mais semelhante à tecnologia de processo de 3 nm da TSMC em termos de densidade de transistores, embora tenha os melhores indicadores de consumo de energia, mas inferior em velocidade. A declaração da IBM é impressionante - no entanto, esta é apenas uma amostra de laboratório, ultrapassando claramente os 3 nm da TSMC apenas no consumo de energia. Ao mesmo tempo, os primeiros lotes arriscados de dispositivos de 3 nm da TSMC aparecerão este ano, e os comerciais no próximo ano.

Em nossa opinião, a TSMC manterá a vantagem em densidade, consumo de energia e velocidade dos dispositivos baseados na tecnologia de processo de 2 nm quando entrarem em produção em 2023-2024.