Paradigma

É muito importante enfatizar aqui que o código de máquina deve parecer, em uma percepção subjetiva relativamente fluente, como um pseudocódigo nos campos das tabelas de despejo e, o menos possível, dar a esotericidade de quaisquer campos de bits.

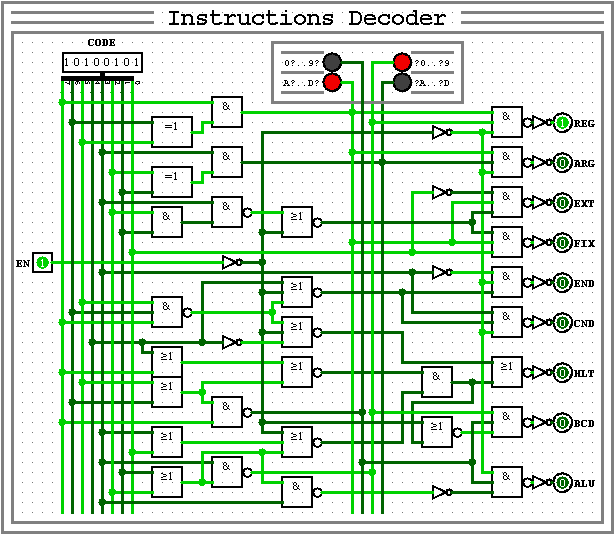

Decodificador de Comando

Um dos elementos mais importantes e chaves de qualquer autômato é um dispositivo para decodificar exatamente aquela ação em um determinado momento no tempo que o próprio programador tinha em mente ao compor a ordem desses comandos em seus algoritmos.

Primeiramente, é necessário fazer um esboço do decodificador Koda-Koyaaniskatsi em Logisim , utilizando as portas lógicas mais acessíveis da nomenclatura da série TTL produzida para garantir a fácil montagem do decodificador em microcircuitos reais.

Aqui apresentamos uma Designação Gráfica Condicional para o decodificador, que é necessária para garantir a compactação e clareza de todo o circuito da máquina no futuro, bem como para verificar o correto funcionamento da decodificação de todos os 256 códigos de instrução.

Registros de prefixo atemporais

Quando o teste visual de desempenho do decodificador correu bem e sem falhas visíveis, era hora de conectar os registros principais para armazenar os índices de RONs ativos, que são disparados pelos comandos do grupo REG como prefixos arquitetônicos.

Para garantir o armazenamento dos vetores de roteamento de dados pelas instruções ALU e RAM, mais um registrador e dois multiplexadores vinculados são adicionados, com os quais você pode conectar registradores arbitrários de qualquer grupo como operandos de instrução.

Por si só, esses registros não se destinam a armazenar os resultados dos cálculos e desempenhar uma espécie de papel como ponteiros para os registros necessários, a fim de fornecer uma interação controlada no programa entre todos os RON e / ou memória disponíveis.

Condição arquitetônica

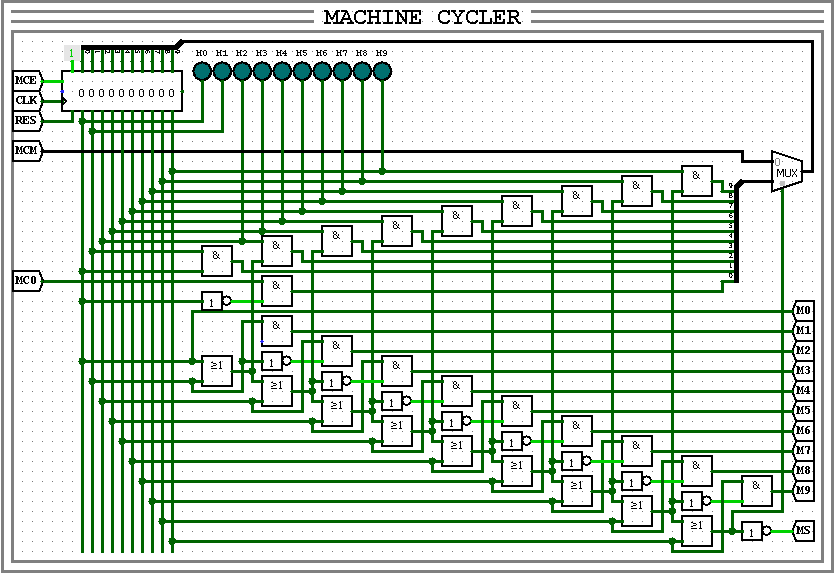

Garantir a interação normal do software de todos os registros requer um Arquivo de Registro de duas portas, que não está incluído nas bibliotecas do Logisim, o que nos obriga a procurar outras soluções alternativas mais ou menos onerosas. O Koyaaniskatsi clássico possui um Arquivo de Registro bastante complexo, que não é considerado aqui como um exemplo ilustrativo e requer o desenvolvimento de uma nova solução para organizar um Arquivo de Registro multiciclo com acesso lento. Uma vez que o esquema acabou sendo de um ciclo, é muito difícil organizar o Arquivo de Registro na RAM aqui e se torna necessário construir um esquema de vários ciclos com muitos ciclos especiais substituindo uns aos outros em uma ordem estritamente especificada.

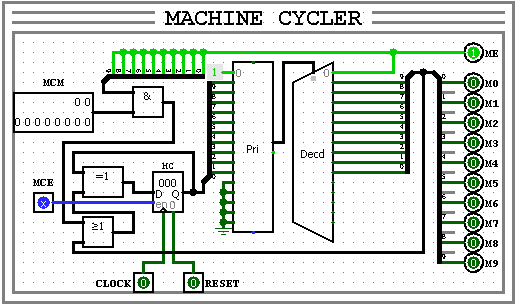

A expressão algorítmica do contador de ciclos pode ser descrita como "m & = m - 1" com desligamento sequencial de todos os bits ativos do estado arquitetônico, onde em um determinado momento do Ciclo da Máquina apenas os nós-chave do circuito são ativados.

O protótipo expandido ao máximo do Contador de Ciclos da Máquina pode ser representado em um esboço de um circuito semelhante, o que é bastante difícil de entender a lógica de seu funcionamento.

Um esboço semelhante pode servir como a opção mais ideal e universal:

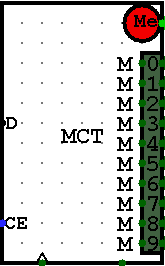

E para uso no esquema, a Designação Gráfica Condicional pode ser a seguinte:

Com a ajuda das portas lógicas 3-OR, agora é possível traduzir o sinal de cada um dos comandos na máscara de bits dos ciclos necessários à correta execução do comando, durante todo o período de execução do qual o contador de comandos ficará temporariamente suspenso.

Conclusão

Então, como você pode ver, para pelo menos começar a entender as nuances da construção independente de uma máquina programável, precisamos apenas passar por até mesmo um conhecimento básico nos níveis de desenho do esquema de uma guirlanda de árvore de Natal piscando. Aqui, nenhum material de referência conhecido por todos foi deliberadamente utilizado, para que o processo criativo fosse mais estimulante e livre de todas as tendências e tendências mundiais, não prestando atenção a todos os possíveis erros de cálculo ou equívocos.

Na próxima parte tentarei continuar minha construção passo a passo do "processador akyn",

já que o novo rascunho está quase funcionando para mim, mas decidi redesenhar do zero

e ao mesmo tempo documentar todas as etapas principais ...