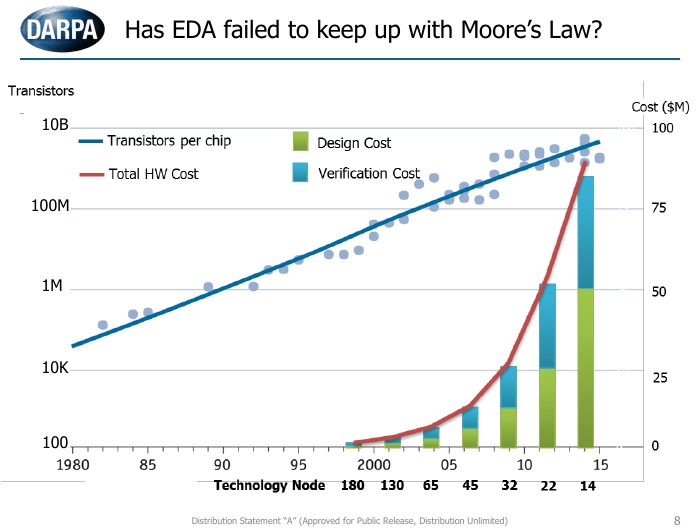

A metodologia usada atualmente para o projeto de VLSI usando linguagens de descrição de hardware tem desvantagens geralmente reconhecidas, a saber:

O desenvolvimento de VLSIs complexos requer centenas de engenheiros qualificados, vários anos de trabalho e bilhões de dólares em custos.

Quase metade do tempo de desenvolvimento é gasto na localização e eliminação de erros no modelo de software do microprocessador projetado.

Custos de mão de obra substanciais são necessários para alcançar alto desempenho em termos de área, produtividade e eficiência energética.

Ideias nacionais e estrangeiras, soluções para problemas de design VLSI, encontram-se dentro do paradigma geralmente aceito, o uso de linguagens de programação para descrever o equipamento projetado. Todas essas soluções são usadas em programas DARPA atualmente implementados .

Programas DARPA

No âmbito da Electronics Resurgence Initiative anunciada pela DARPA, a tarefa foi definida para superar os problemas da metodologia aplicada para projetar sistemas microprocessados. Para tanto, as seguintes sub-rotinas são implementadas:

CRAFT - envolve a criação de ferramentas de síntese de VLSI de alto nível;

IDEA - visa criar um gerador automático de layout SoC, microcircuitos multichip, placas de circuito impresso;

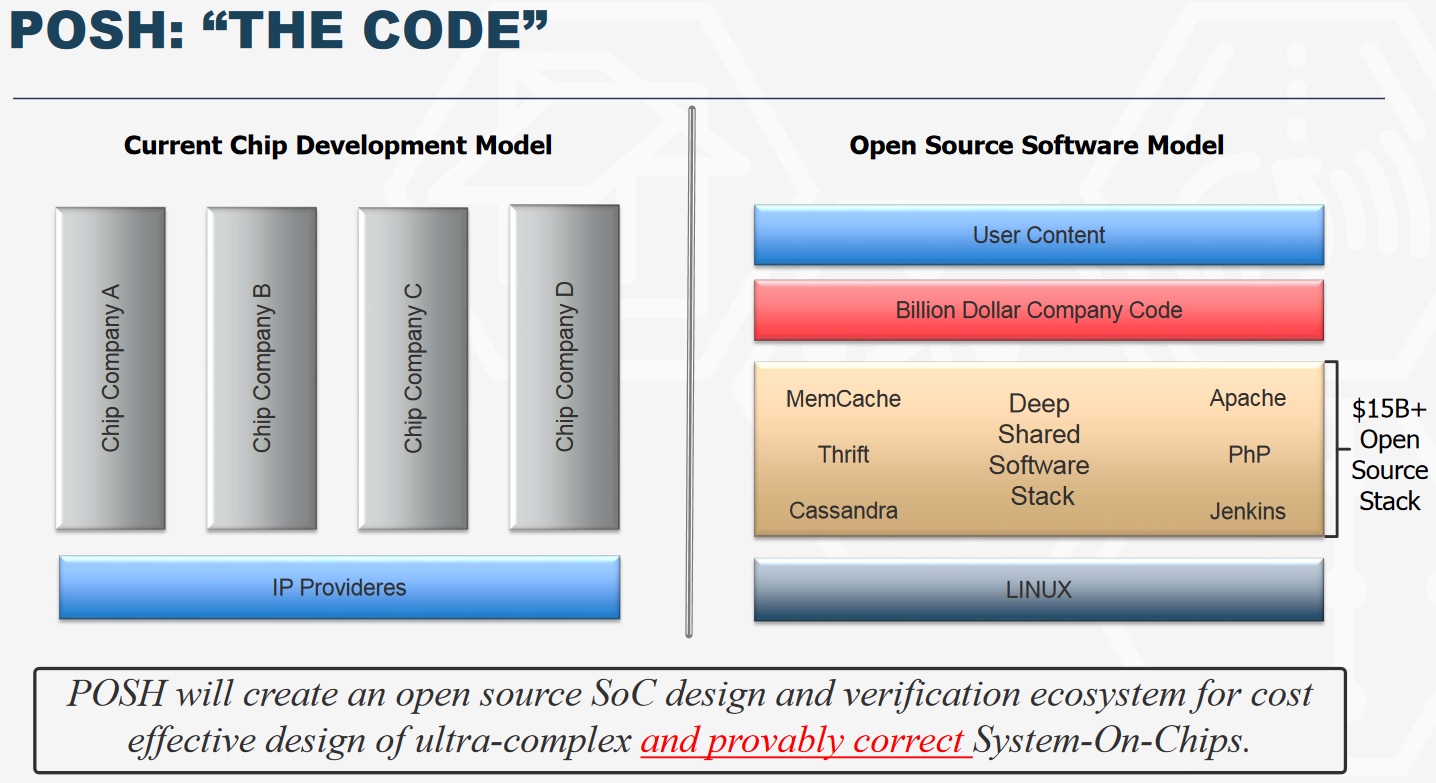

POSH - visa criar um projeto de hardware de código aberto viável e um ecossistema de verificação que projetará SoCs ultracomplexos de maneira econômica.

Em caso de execução bem-sucedida desses programas, os resultados obtidos devem ser combinados em sistemas CAD avançados. Espera-se que ele alcance um crescimento de 10 vezes na velocidade de desenvolvimento em relação à criação manual de código RTL. Além disso, o objetivo é mudar fundamentalmente a prática de desenvolvimento de dispositivos microprocessados. O objetivo final de transformar a prática de engenharia é descrito a seguir :

.

, .

, DARPA ( Electronics Resurgence Initiative Page 3 Investments Design Thrust). , , , , , , , . , SoC, . , , SoC, (SiP). , .

CRAFT ( Khailany Brucek CRAFT Final ERI Summit 2019):

:

a. , , C ++ Verilog;

b. ;

c. , , MatchLib.

AGILE :

a. , , , VLSI (Very Large Scale Integration);

b. ;

c. AGILE ;

d. ++ .

« SoC. , - SystemC ++. (GALS) . 16- FinFET, ». (A Modular Digital VLSI Flow for High-Productivity SoC Design”, Khailany et al., DAC 2018)

Spoiler

1. CRAFT [1].

IDEA . , , SoC SiP. , , (COTS). COTS , SiP IP- SoC. , , . , SoC SiP.

Spoiler

2. , IDEA [5].

, , IDEA, . IDEA 3.

Spoiler

3. IDEA [5].

POSH , . DARPA . , . , , . , POSH , SoC . , , (IP ) .

, SoC, . , , . , . , .

, , IP SoC. , ( ) . , , , , .

Spoiler

4. SoC POSH [4].

POSH SoC, . , , , , IP SoC.

: « , , ».

, ERI Summit 2019, .

, CRAFT :

8-11 .

4.3-5.3 16- GF, - ASIC.

:

POSH , : « , , , , ».

, , IDEA, . , ( ).

, (ASIC), , . . , , , , - .

, , , , . , , .

, DARPA:

. .

, .

.

– .

, COTS, IP , . , . , SoC SiP , , DARPA.

, . , .

2019 NVIDIA [6]. NVIDIA Orin 2022 . , Orin , , NVIDIA [32]. 2000 , 750 .

, , , , , .

, , , , . , , DARPA DOE, [25]:

;

;

.

SoC SiP , .

, Neocortex, DCIGN RNN – , , . , 2020 [37]. Cerebras CS-1 HPE SuperDome Flex . Cerebras CS-1 Cerebras. 300- [2].

, , 3D TSV. , , IBM [16], , [22].

Spoiler

5. IBM [16].

,

, 6, Brucek Khailany (Director of research, ASIC & VLSI NVIDIA Corporation).

Spoiler

6. [1].

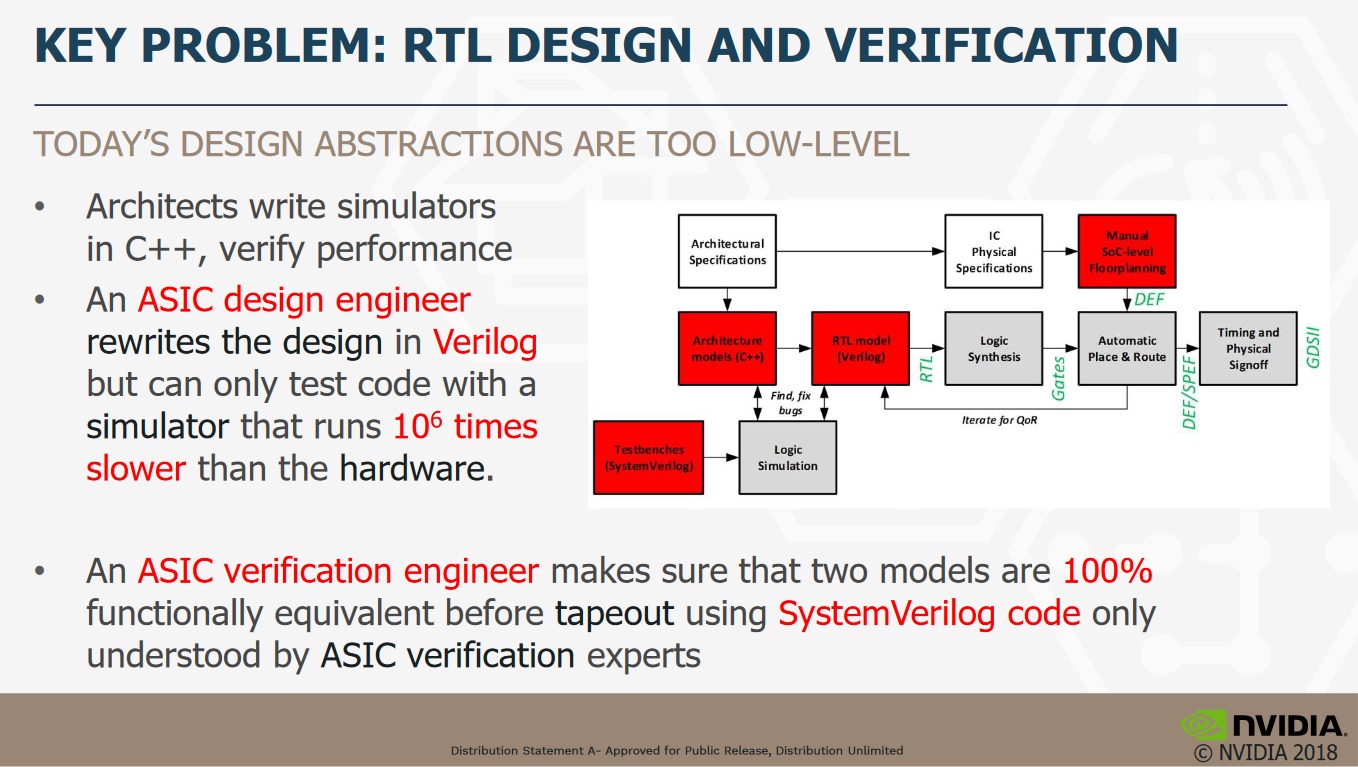

, , (HDL), .

(HDL). , , (RTL), (Logic Synthesis). . , (physical design).

, , . 7.

Spoiler

7. [23].

, (SiP) . - , - .

. , , , .. . , . .

, , , .. , . . , , .

, , , . 8.

Spoiler

8. , .

, , , .

, , NVIDIA Xavier 8000 - [1].

Jensen Huang, NVIDIA V100 , , 3 [7].

, , . . 9 , .

, .

Spoiler

9. [7].

, , . . DARPA , , . , , .

. , . [30].

, , , . , .

, , , , . , - , .

, .

( ) , , . .

( ) , .. . ( ) , .

, , , .. , .

( ), , . , .

, ( ) . , , , , , , . , ( ) .

.

( ) , [20]. . .

, , , [33].

. , , – [34].

, , , , , . , . , , [17, 27].

, , , , [15].

- . , , , , [30].

, , . , , . , ( ) ( ) , [10, 12].

.

, , , , .

– . , , . , .

( ) . .

, ( ).

. , .

, , , , .

, , . , , .

, .

, , .

(.. .). , , , , , .

( ), . « », « », « ». , [29].

, (.. ) .

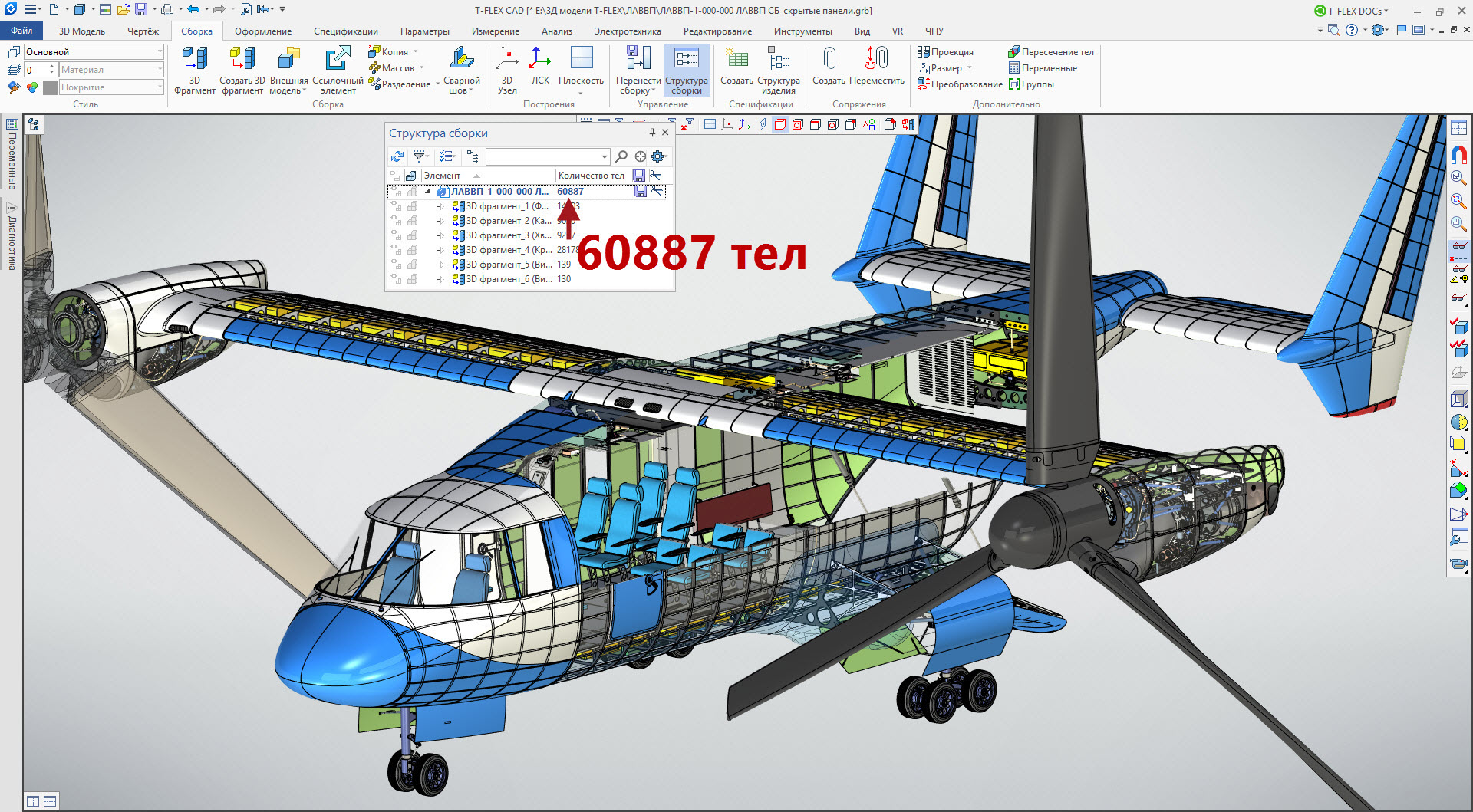

. , , T-FLEX CAD 16 (. . 10). 60 000 , . 2- 6 [31].

Spoiler

10. T-FLEX CAD 16.

, , , , .

, . . . (. . 11).

Spoiler

11. .

, , . , .

, .

, , (. . 8), .

, , .

. , , (. . 6).

, , . .

, ( ). , , . .

, .

. HDL . HDL . , , .

[23]:

, sizing/physical/logic synthesis. .

, , .

NP- – , , , [24]. , , « » — . , .

, IDEA, , , (. . 2). (. . 3).

HDL , , , , , . , , (. . 6). .

. , .

. , . , .

, , , . , , , ( , , ), .

( ) , , . , , , , .

, , – (. . 12).

Spoiler

12. SystemVerilog [13].

, , .. , ( ).

, [33].

( ), . , [17, 27]. , (software engineer) .

, . . , , , . , . . , , .

HDL, , . , , . . .

- .

– - ().

, , DARPA. - .

-, , , . , ( , ), . , , , .

-, ( ) , .. . , . , , . , , .

, DARPA , . , (SoC & SiP) .

, , .

, , - .

, . «», .., , . , . , , . , , Verilog, , . , INTEL Corp., Kevet ( ). RTL , , 6 . RTL , , 20 .

, , .

, T-FLEX CAD 16, , , , , , .

. «-», , - , , , . . , - , . - , [14, 28, 39].

, , , , . , , .

1. A modular digital VLSI flow for high-productivity SOC design. Brucek Khailany director of research, ASIC & VLSI NVIDIA CORPORATION. ERI Summit 2018.

2. Cerebras ― . . 20.08.2019. https://3dnews.ru/992698 ( : 11.11.2020)

3. DARPA . 04.07.2018 https://3dnews.ru/972103 ( 07.05.2019)

4. IDEA & POSH program updates. Andreas Olofsson. DARPA MTO program manager. ERI Summit 2019.

5. Intelligent Design of Electronic Assets (IDEA) & Posh Open Source Hardware (POSH) // Andreas Olofsson Program Manager, DARPA/MTO. Proposers Day Mountain View, CA. 9/22/17.

6. NVIDIA Introduces DRIVE AGX Orin — Advanced, Software-Defined Platform for Autonomous Machines. Tuesday, December 17, 2019. https://nvidianews.nvidia.com/news/nvidia-introduces-drive-agx-orin-advanced-software-defined-platform-for-autonomous-machines ( : 11.11.2020)

7. Silicon Compilers - Version 2.0 // Andreas Olofsson Program Manager, DARPA/MTO. International Symposium on Physical Design. March 25-28, Monterey, CA. 2019.

8. .., .. : . . . , . – . 2003.

9. . . // Chip News – 2003. -№4.

10. : / . . . , . . . -2- ., . . -. : -, 2016.

11. ., ., . : . . – 2013. -№07 http://www.osp.ru/os/2013/07/13037342/ ( 05.11.2013)

12. 10075-2011 . .

13. . SystemVerilog / . . . . , . . , . . ; . . . . , . . . – .: , 2019.

14. [ ]: . . https://ru.wikipedia.org/wiki/ ( : 11.11.2020)

15. . . . — .: , 2008. 16. . / .., ... 5- . 21 2014 .

17. . . . . . 2. № 2. 2012.

18. ? .. « : » , 7-13 2015. https://scorcher.ru/articles/images/3678/anokhin.pdf ( 08.09.2019)

19. ., . SystemC “ ”. // Chip News – 2006. -№9.

20. : . .. . «». 27 , 2016.

21. . "" . . BBC NEWS . 5 2019. https://www.bbc.com/russian/features-48583773 ( : 11.11.2020)

22. 100 . 01.03.2019 https://3dnews.ru/983605 ( : 05.05.2019)

23. .., .. . [ ] http://mk.cs.msu.ru/index.php/_____ ( : 15.10.2013)

24. . : . . 2013.

25. : , , . / .., .. 01.11.2012

26. : / . . , . . . — 3- ., . . — . : , 2017.

27. . . . BECTH. MOCK. -. . 14. . 2007. № 2.

28. . . : – ! – .: , 2001.

29. -. . . // , . 6 / . . . , . . . – .: « », 2014.

30. , . .. // « » № 1 2011.

31. T-FLEX CAD 16 ( 60000 ). T-FLEX CAD. 25.11.2019. https://3dtoday.ru/blogs/topsystems/proekt-tyazhelogo-konvertoplana-v-t-flex-cad-16-bolee-60000-tel ( : 11.11.2020)

32. NVIDIA Orin 12- Samsung. . 19.12.2019. https://3dnews.ru/1000054 ( : 11.11.2020)

33. . .. — .: , 2005.

34. : , , . . . : , , № 3 2014.

35. . «» 14 . 01.03.2012 . http://compulenta.computerra.ru/archive/neuroscience/664455/ ( : 15.10.20013)

36. .. . – 2- . - .: «», 2005.

37. Neocortex: 800 . Cerebras . . 09.06.2020. https://servernews.ru/1013005 ( : 11.11.2020)

38. 200 7- CPU AMD EPYC Rome. 15.12.2018 https://servernews.ru/979696 ( : 07.06.2019)

39. – [ ]: . . https://ru.wikipedia.org/wiki/_—_ ( : 11.11.2020)