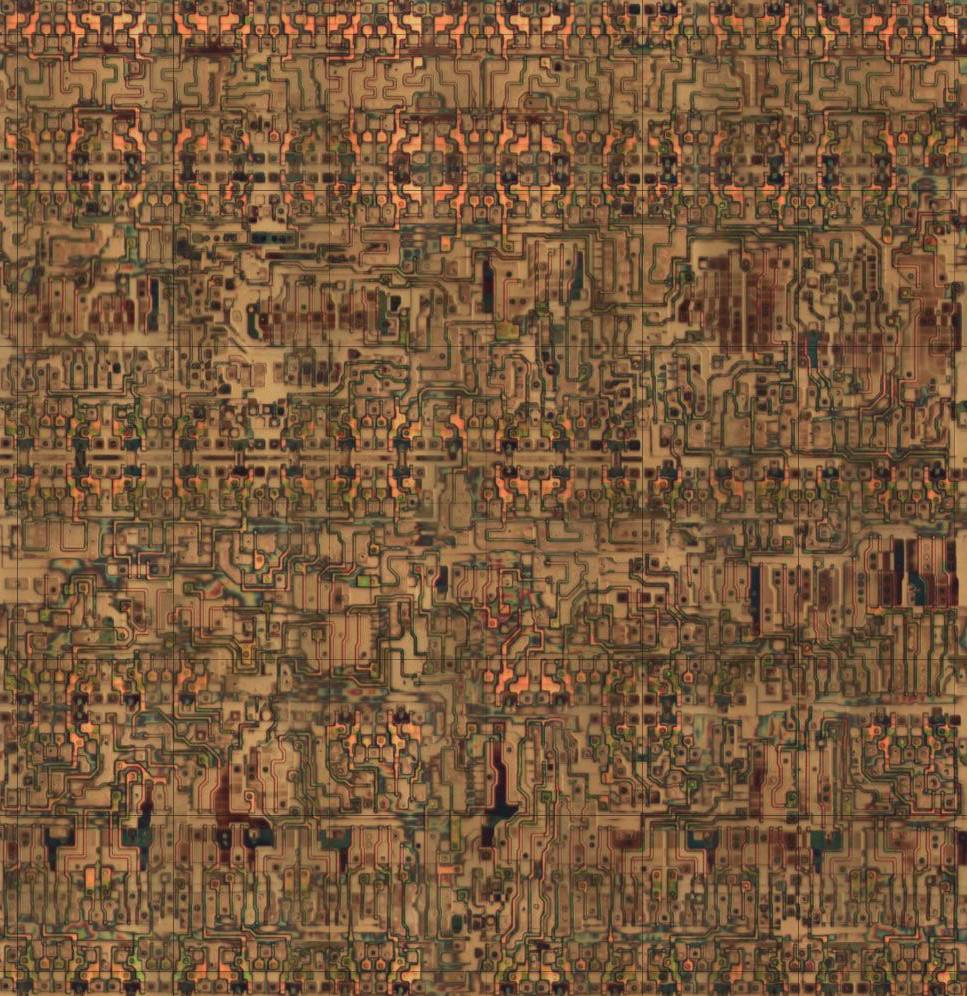

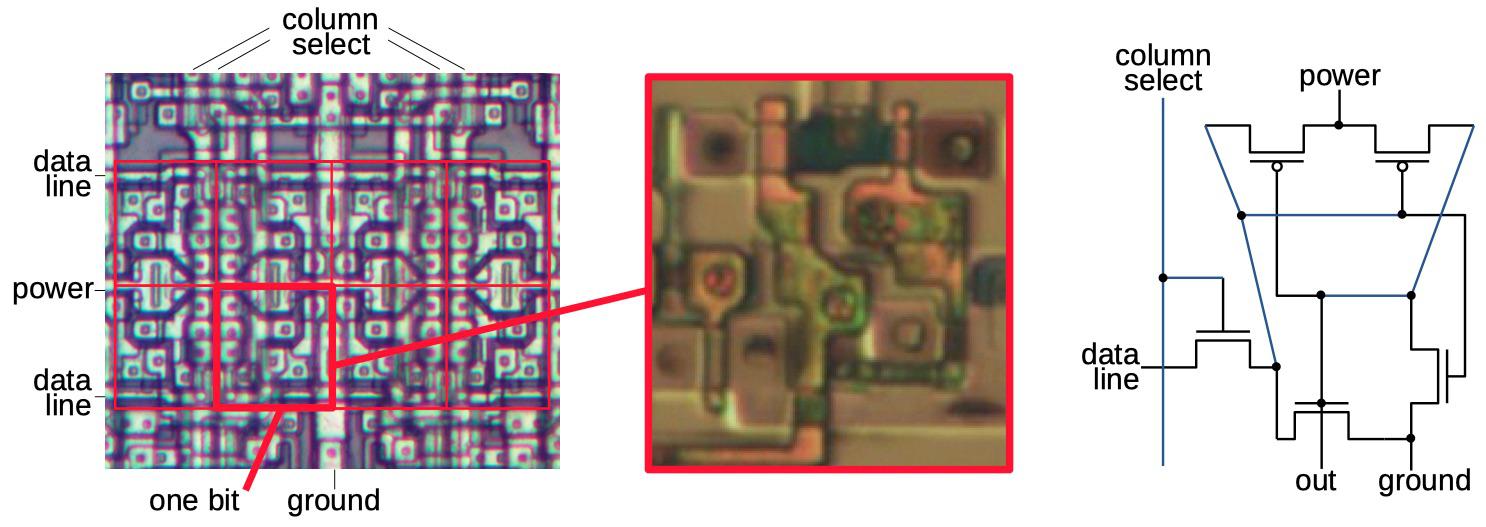

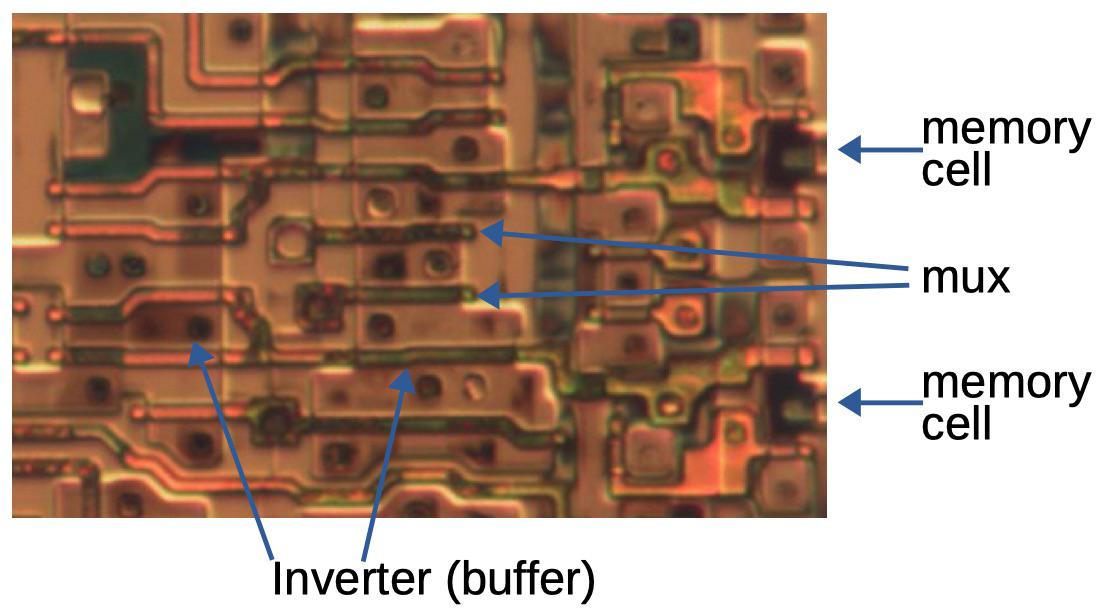

A fotografia mostra um dos 64 blocos do chip XC2064. As camadas de metalização são removidas, podemos ver os transistores de silício e polissilício sob a metalização. Você pode ver uma foto em escala maior aqui: siliconpr0n .

O FPGA foi inventado por Ross Freeman, co-fundador da Xilinx em 1984, o primeiro FPGA foi o XC2064. Era muito mais simples do que os FPGAs modernos, continha apenas 64 blocos lógicos, em comparação com os milhares e milhões dos FPGAs modernos, e sua criação levou ao surgimento de uma indústria que valia bilhões de dólares. O XC2064 é tão importante que entrou no Chip Hall of Fame. Eu fiz a engenharia reversa do XC2064 e neste post eu explico sua estrutura interna em termos gerais e como ele é programado com um bitstream.

Xilinx

Xilinx -. , , Xilinx , . Xilinx Seiko Epson Semiconductor Division ( Seiko Epson).

XC2064

: ( ) . — (Programmable Logic Devices, PLD), , , 1967 . , , , . , PROM, , , EPROM, . , , Programmable Logic Array, Programmable Array Logic (1978), Generic Array Logic Uncommitted Logic Array. , , « », . , , , , , . , . "Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology." "A Brief History of FPGAs".

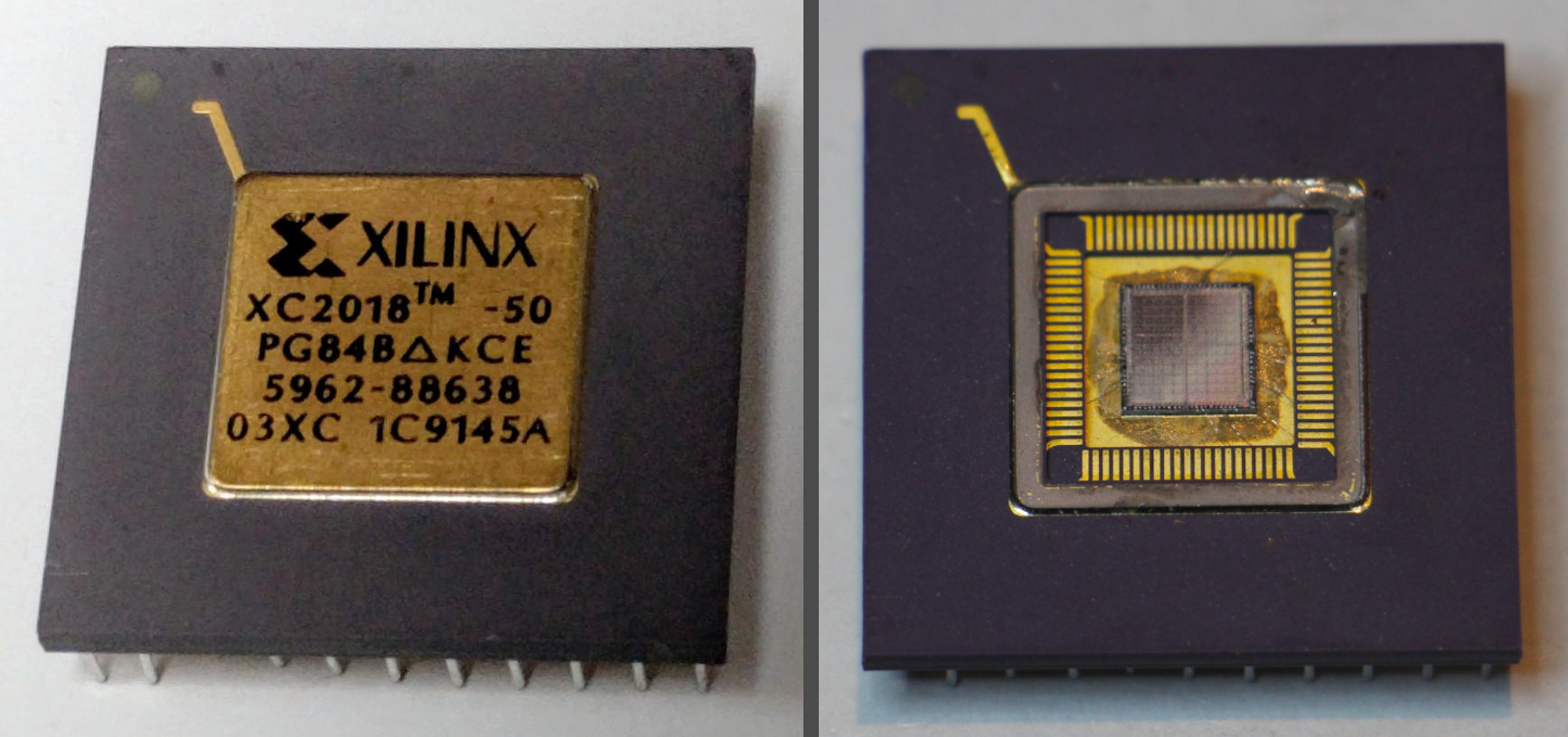

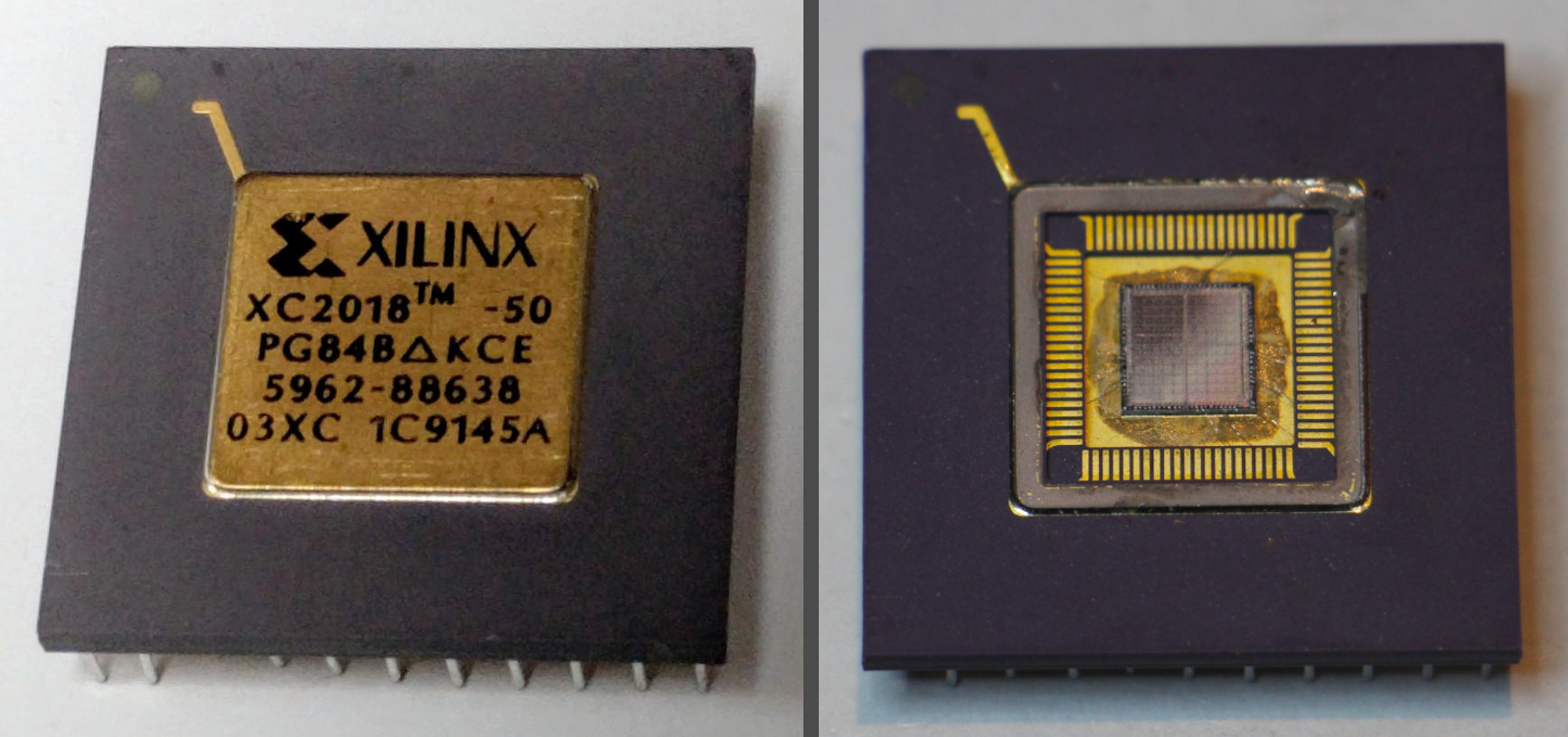

Xilinx XC2064 é o primeiro chip FPGA. Retirado daqui: siliconpr0n .

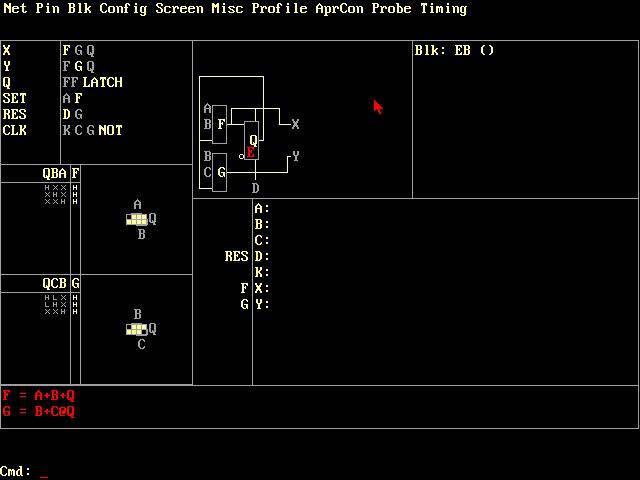

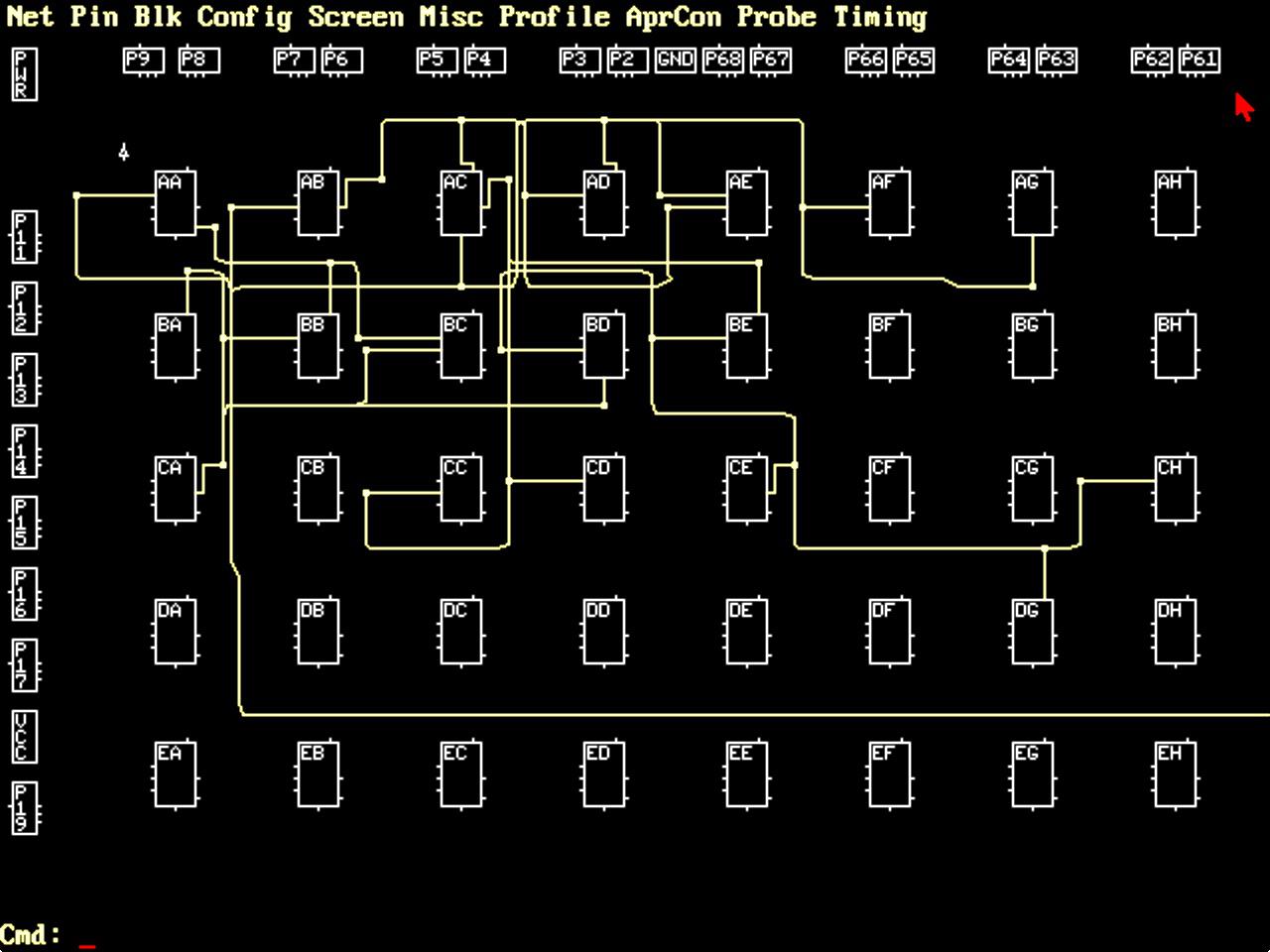

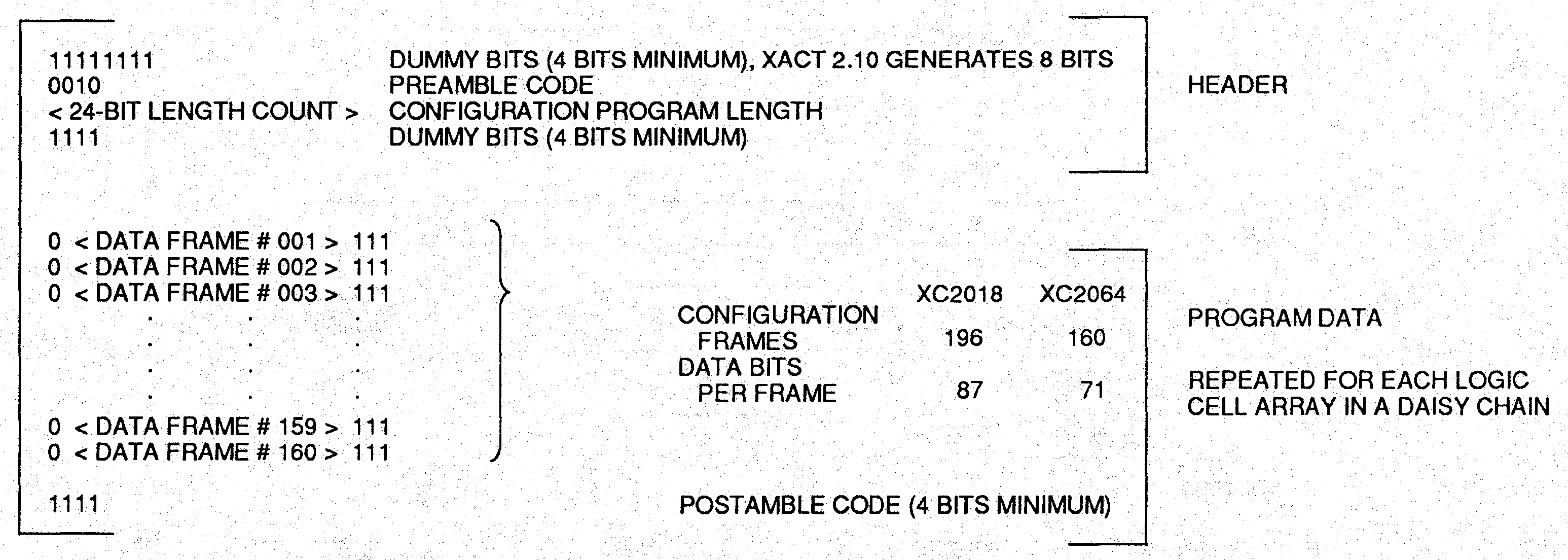

Os FPGAs são atualmente programados em linguagens de descrição de hardware como Verilog ou VHDL, mas na época, a Xilinx fornecia seu próprio software de desenvolvimento, um aplicativo MS-DOS chamado XACT, por US $ 12.000. O XACT funcionava em um nível inferior ao das ferramentas modernas: o usuário definia a função de cada bloco lógico, conforme mostrado na imagem abaixo, e as conexões entre os blocos lógicos.

O XACT roteava as conexões e gerava um arquivo de configuração (fluxo de bits) que era carregado no FPGA.

Captura de tela do XACT. As duas tabelas F e G implementam as equações mostradas na parte inferior da tela, com o mapa de Karnaugh mostrado acima.

O FPGA foi configurado usando um bitstream, uma sequência de bits em um formato proprietário. Se você observar o fluxo de bits XC2064 (abaixo), verá uma mistura misteriosa de padrões que se repetem de maneira irregular e estão espalhados por todo o fluxo de bits. No entanto, estudar os circuitos físicos do FPGA revela a estrutura de dados do fluxo de bits e ela pode ser estudada.

Parte do fluxo de bits gerado pelo XACT.

Como funciona o FPGA?

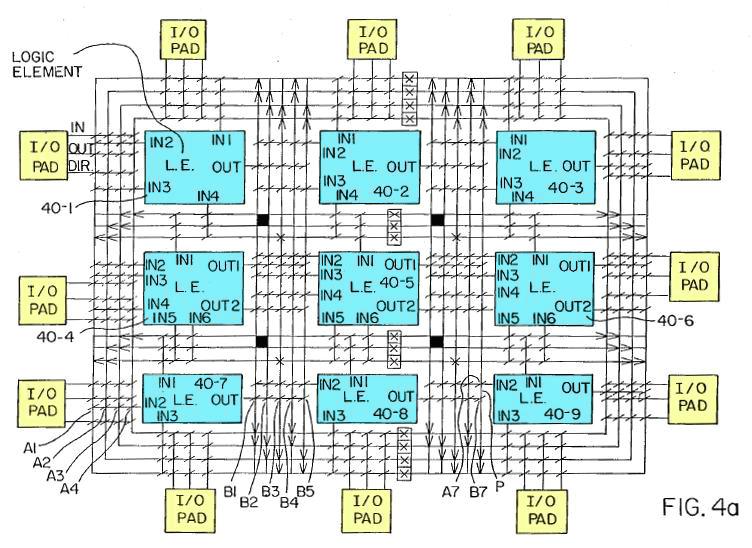

A figura abaixo, retirada da patente original do FPGA, mostra a estrutura básica de um FPGA. Este FPGA simplificado tem um total de 9 blocos lógicos (marcados em azul) e 12 portas de E / S. Uma rede de interconexão conecta componentes. Definindo interruptores (linhas diagonais) nas conexões, os blocos lógicos podem ser conectados entre si e às portas de E / S. Cada elemento lógico pode ser programado para a função lógica necessária. Como resultado, esse chip programável pode implementar qualquer dispositivo que se encaixe no espaço disponível.

Patente FPGA , blocos lógicos (LE) interconectados.

Bloco lógico configurável (CLB)

Embora a imagem acima mostre 9 CLBs, o XC2064 possui 64 CLBs. A figura abaixo mostra a estrutura do CLB. CLB tem 4 entradas (A, B, C, D) e duas saídas (X e Y). No meio está a lógica combinatória, que pode ser programada para qualquer função lógica desejada. O CLB também contém um gatilho, cuja presença permite implementar contadores, registradores de deslocamento, máquinas de estado e outros circuitos com estado. Os trapézios indicam multiplexadores que podem ser programados para transmitir um sinal de qualquer uma das entradas. Os multiplexadores permitem que você configure o CLB para uma tarefa específica selecionando sinais específicos para controlar o acionador e as saídas.

Bloco lógico configurável em XC2064, retirado daqui: ficha técnica .

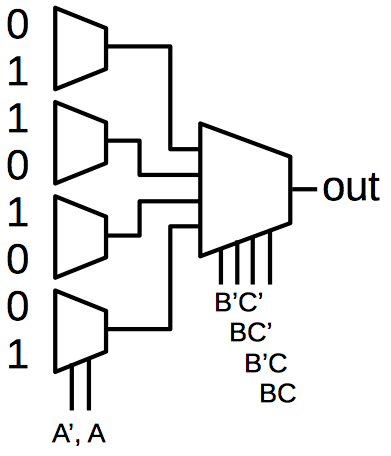

Você pode estar se perguntando como a lógica combinacional implementa funções lógicas arbitrárias. Existe uma escolha entre um conjunto de AND, OR, XOR e assim por diante? Não, existe um truque inteligente chamado tabela de pesquisa (LUT), que é na verdade a tabela verdade para a função. Por exemplo, uma função de três variáveis é definida por uma tabela de 8 linhas. O LUT contém 8 bits de memória. Podemos implementar qualquer função lógica de 3 entradas, mantendo esses três bits.

Ver tabelas

XC2064 — , . CLB . XC2064 , 4 . , .

XC2064 . .

XC2064 . .

Conexões

O próximo aspecto principal dos FPGAs são as conexões, que podem ser programadas para alternar o CLB de várias maneiras. As conexões são complexas, mas a descrição aproximada é que existem segmentos de conexões verticais e horizontais entre todos os CLBs. Você pode conectar o CLB a linhas horizontais e verticais e criar conexões arbitrárias. Um tipo de conexão mais complexo é a "matriz de comutação". Cada matriz possui 8 pinos que podem ser conectados entre si (quase) de qualquer forma.

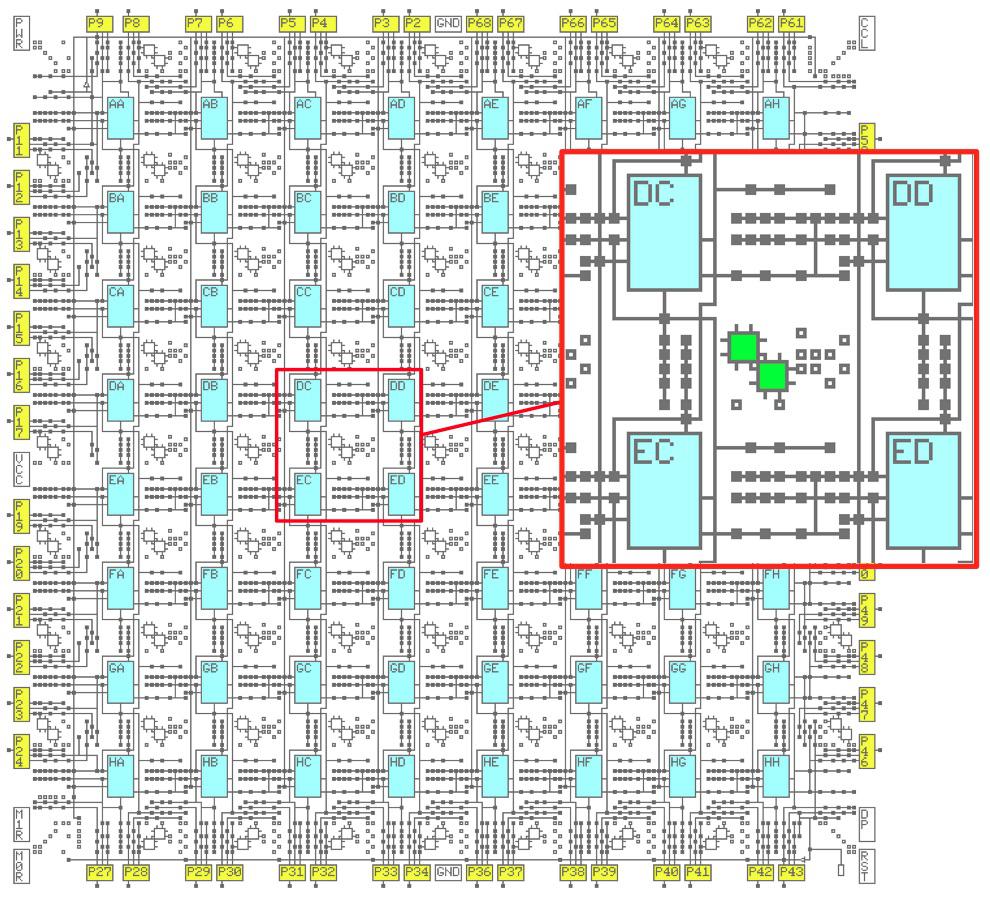

A figura abaixo mostra a estrutura dos links XC2064 que fornecem conexões entre blocos lógicos (azul) e linhas de E / S (amarelo). A inserção mostra os detalhes do mecanismo de acoplamento. Os retângulos verdes são matrizes de chave de 8 pinos e os pequenos quadrados são pontos de conexão programáveis.

O FPGA XC2064 possui uma matriz CLB 8x8. Cada CLB tem um nome de AA a HH.

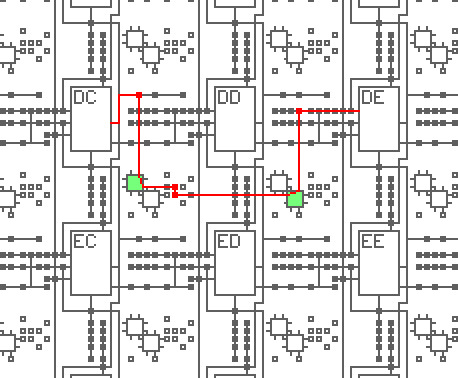

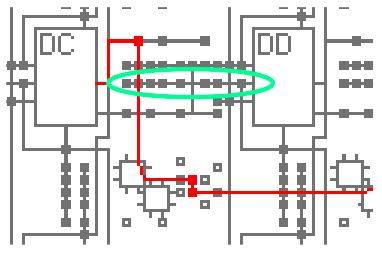

A conexão pode mudar, por exemplo, a saída de um bloco DC para uma entrada de um bloco DE, conforme mostrado abaixo. A linha vermelha mostra o caminho do sinal e os pequenos quadrados vermelhos mostram os pontos de conexão ativados. Saindo do bloco DC, o sinal é roteado para o primeiro ponto de conexão em um switch de 8 pinos (verde), que o encaminha através de dois pontos de conexão e outro switch de 8 vias (linhas verticais e horizontais não utilizadas não mostradas). Observe que a conexão é bastante complexa, mesmo um caminho tão curto usa quatro pontos de conexão e dois switches.

Exemplo de roteamento de sinal da saída de um bloco DC para um bloco DE.

A captura de tela abaixo mostra como o rastreamento é feito no XACT. As linhas amarelas mostram conexões entre blocos lógicos. À medida que o número de sinais aumenta, torna-se difícil fazer conexões sem conflito entre os caminhos. O XACT rastreia automaticamente, mas o rastreamento também pode ser editado manualmente.

Captura de tela do programa XACT. É um programa do MS-DOS controlado pelo teclado e mouse.

Implementação

A seguir, veremos os circuitos internos do XC2064 por engenharia reversa de uma foto do cristal. Aviso que isso requer alguma familiaridade com o XC2064.

Foto de cristal

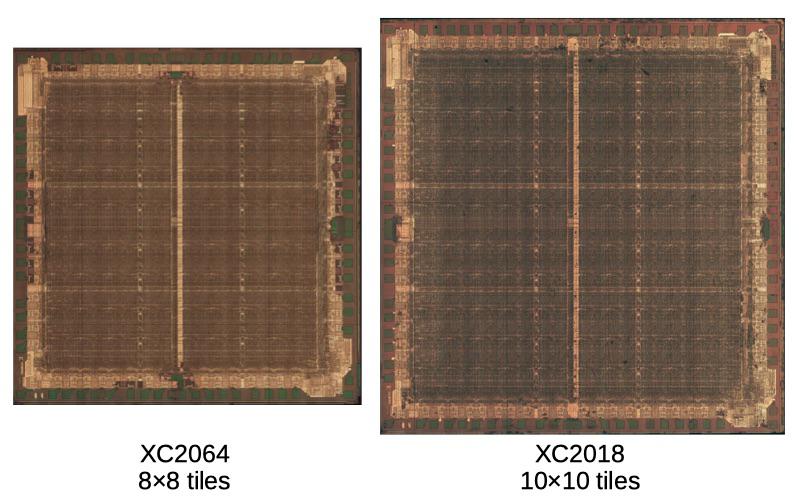

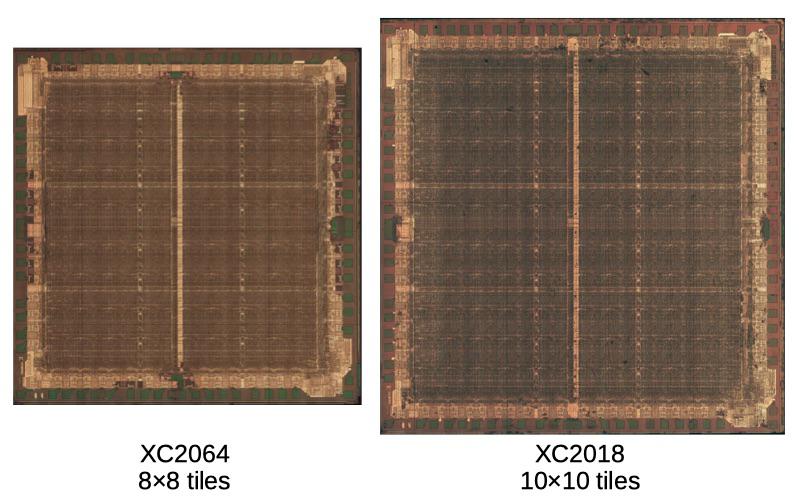

XC2064 XC20186, XC2064 XC2018 siliconpr0n. , . John McMaster , , . , .

XC2064 , John McMaster.

XC2064 , John McMaster.

XC2018

Xilinx XC2018 ( ) 100 , , XC2064. , XC2064 64 , 1010, 88. XC2018 , .

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

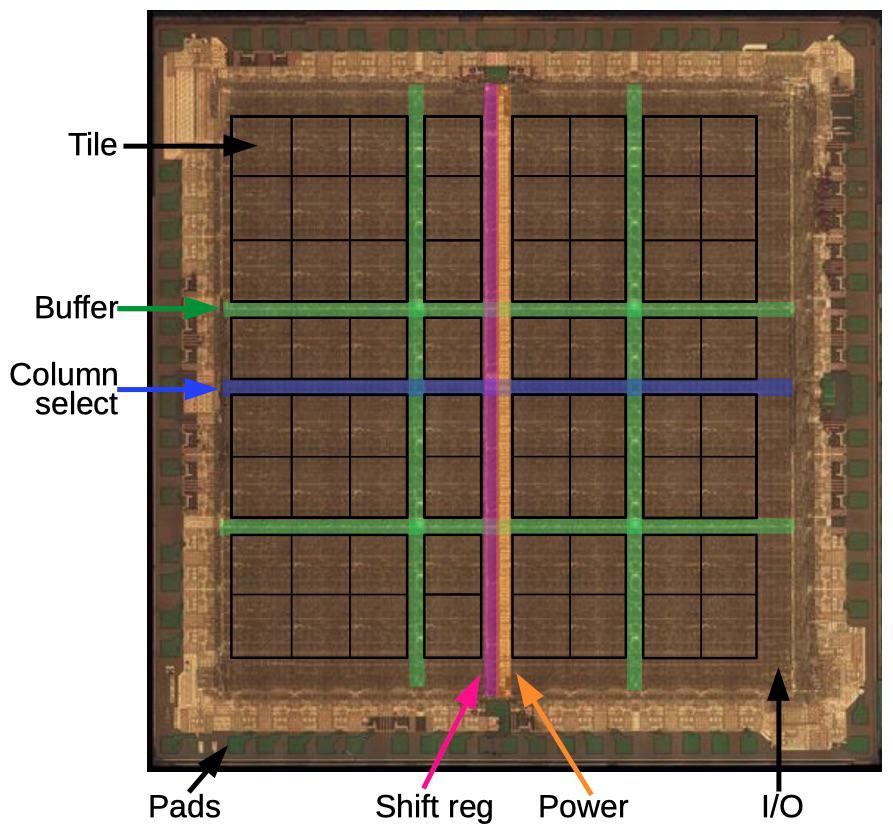

Abaixo está uma foto do cristal XC2064. A parte principal do FPGA é uma matriz de blocos de 8x8, cada um dos quais contém um bloco lógico e circuitos circundantes. Embora o diagrama FPGA mostre blocos lógicos (CLBs) separados dos diagramas de fiação da entidade, na realidade este não é o caso. Na verdade, cada bloco lógico e seu ambiente são implementados como um único nó, um bloco. (Para ser mais preciso, o bloco inclui conexões na parte superior e esquerda de cada CLB.)

Layout de bloco XC2064. Retirado daqui: siliconpr0n .

Localizados nas laterais do circuito integrado, os blocos de E / S fornecem comunicação com o mundo externo. Eles são conectados aos pinos do cristal, que são mostrados como pequenos quadrados verdes, e conectados aos pinos da caixa do microcircuito. Existem buffers no dado (verde): dois verticais e dois horizontais. Esses buffers amplificam o sinal que viaja por uma longa distância pelo chip e reduzem a latência. O registro de deslocamento vertical (rosa) e a cadeia de busca da coluna horizontal são usados para carregar o fluxo de bits no chip, conforme mostrado abaixo.

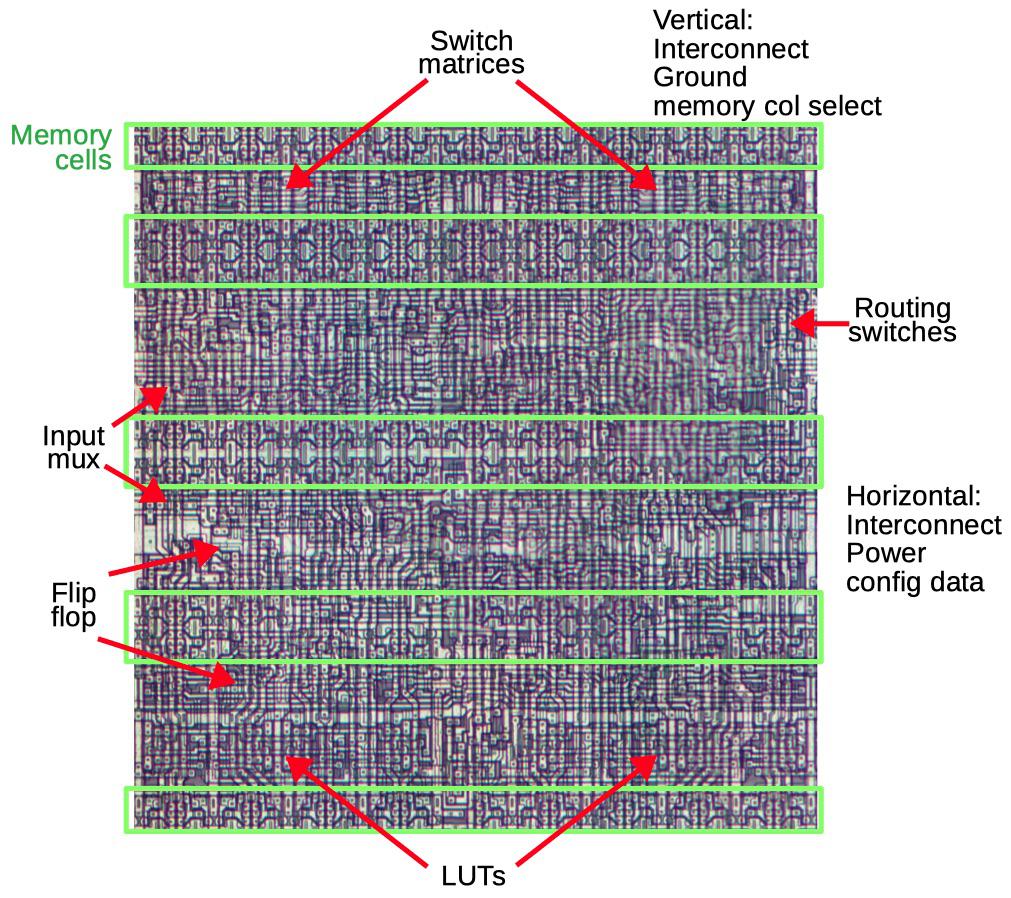

Dentro dos ladrilhos

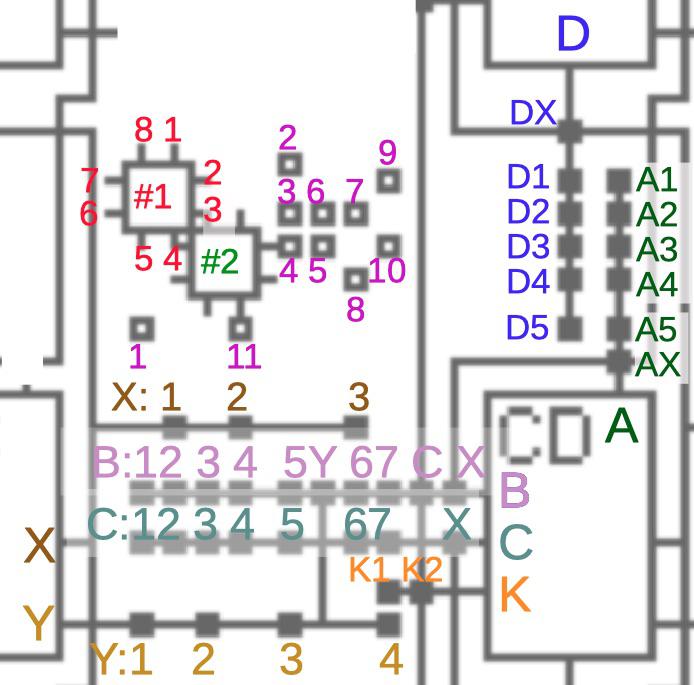

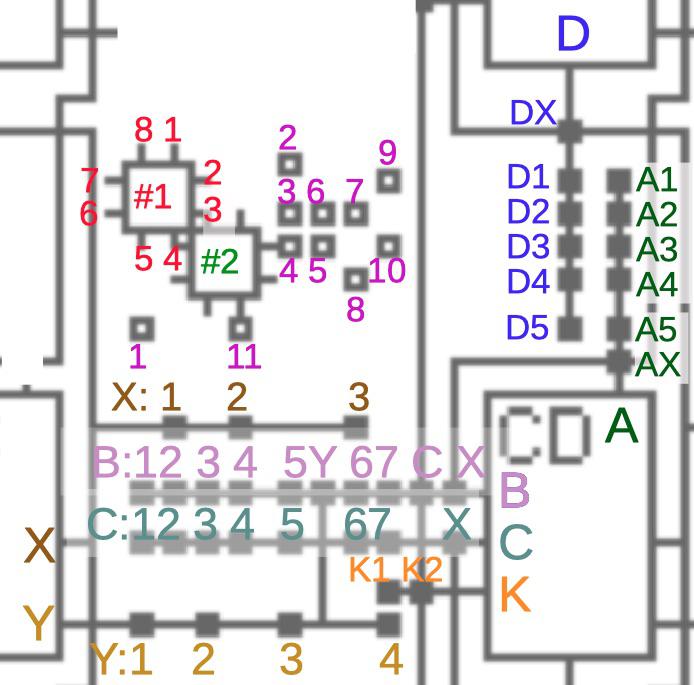

A imagem abaixo mostra a estrutura de um ladrilho XC2064, o chip contém 64 desses ladrilhos empacotados em um dado. Cerca de 40% de cada bloco é ocupado por células de memória (mostradas em verde) que armazenam bits de configuração. O terço superior (aproximadamente) do bloco contém os diagramas de conexão: duas matrizes de switch e vários switches de link individuais. Abaixo está o bloco lógico. A parte principal do bloco lógico é o multiplexador de entrada, flip-flop e tabela de consulta. A placa é conectada aos vizinhos por meio de linhas de comunicação horizontais e verticais e também aos trilhos de alimentação e aterramento. Os bits de dados de configuração entram nos locais da memória horizontalmente e os sinais verticais selecionam uma coluna específica para carregar.

Um bloco FPGA mostrando importantes nós funcionais

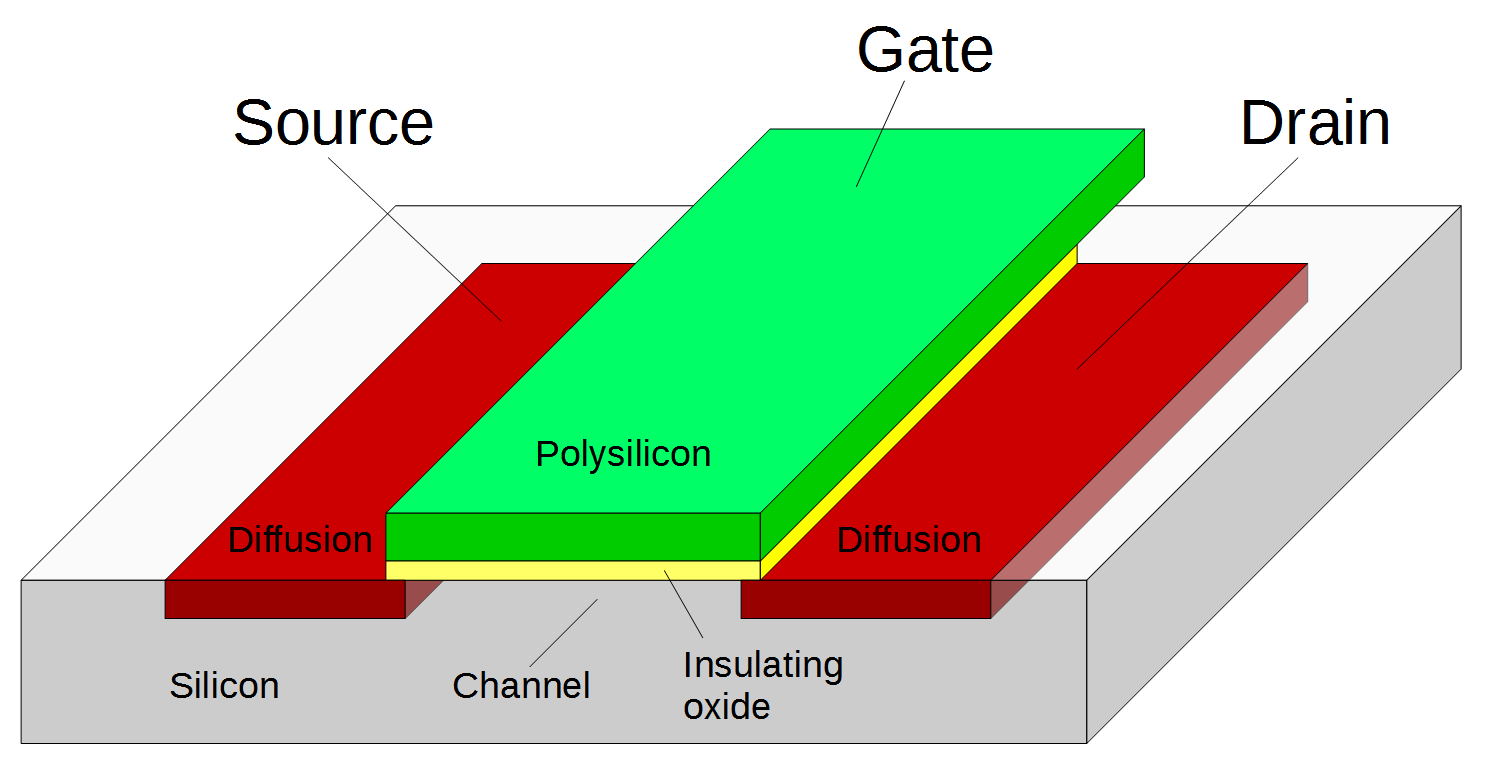

Transistores

FPGA é implementado na lógica CMOS (CMOS), construída a partir de transistores NMOS e PMOS. Os transistores desempenham duas funções principais nos FPGAs. Primeiro, os elementos lógicos são formados a partir de suas combinações. Em segundo lugar, os transistores são usados como interruptores pelos quais um sinal passa, por exemplo, para formar conexões entre blocos. Um transistor que desempenha essa função é chamado de transistor direto. A figura abaixo mostra a estrutura básica de um MOSFET. Duas seções de silício são dopadas com impurezas para criar um dreno e uma fonte. Entre eles está um portão que liga e desliga o transistor e controla a corrente entre o dreno e a fonte. O obturador é feito de um tipo especial de silício chamado polissilício, isolado do silício por baixo por uma fina camada de óxido. Acima dele, existem duas camadas de metalização, que fornecem conexões de circuito.

Estrutura do MOSFET

Na foto do cristal, podemos observar a aparência do transistor em um microscópio. A porta de polissilício é uma linha em serpentina entre duas regiões dopadas de silício. Os círculos são vias que conectam o silicone e a camada de metal (removida nesta foto).

FPGA MOSFET

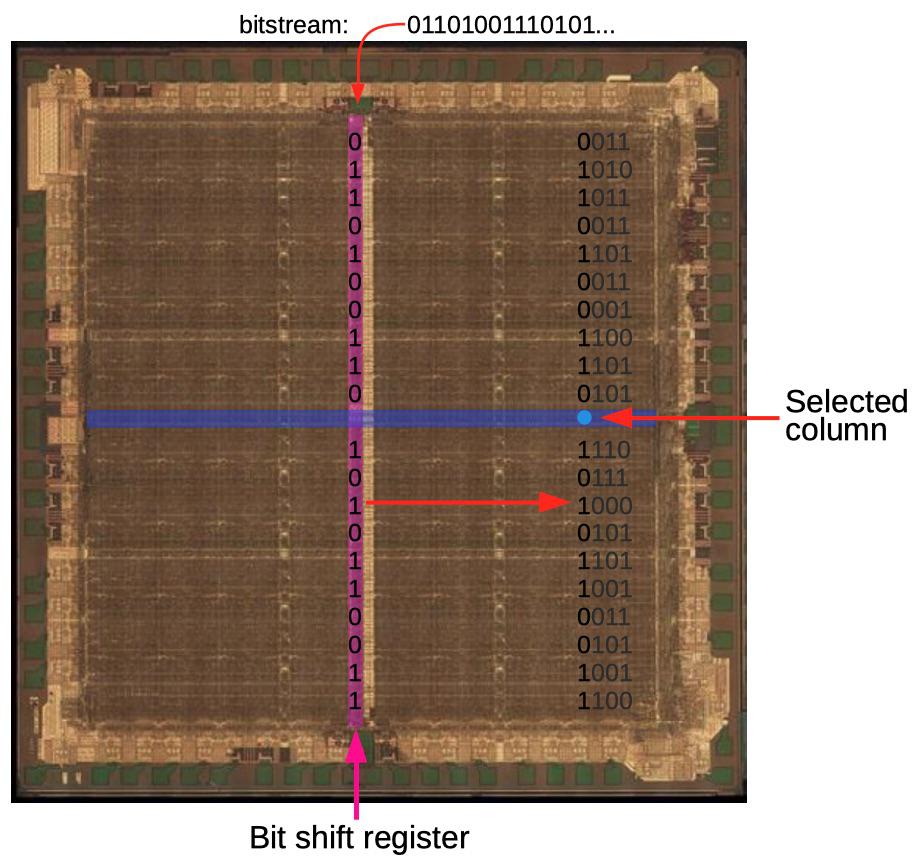

Bitstream e memória de configuração

As informações de configuração no XC2064 são armazenadas nos locais da memória de configuração. O FPGA não usa memória em bloco para isso, ao invés, a memória de configuração é distribuída por todo o cristal na forma de uma grade 160x71, cada bit é colocado próximo ao circuito que ele controla. A figura abaixo mostra o bitstream de configuração carregado no FPGA. O fluxo de bits é carregado em um registrador de deslocamento no meio do chip (rosa). Assim que 71 bits são carregados no registrador de deslocamento, o circuito de busca de coluna (azul) seleciona a coluna de memória desejada e os bits são carregados na coluna em paralelo. Em seguida, os próximos 71 bits são carregados no registrador de deslocamento e a próxima coluna à esquerda é selecionada. O processo é repetido para todas as 160 colunas do FPGA e todo o fluxo de bits é carregado no FPGA. O uso de um shift register elimina a necessidade de grandes circuitos de endereçamento de memória.

Como o fluxo de bits é carregado no FPGA. Bits são mostrados convencionalmente, o armazenamento real de bits é muito mais denso. As três colunas à direita já foram carregadas e a quarta está carregando. A foto do cristal é tirada daqui: siliconpr0n .

O importante é que o fluxo de bits seja distribuído pelo chip exatamente na ordem em que os bits aparecem no arquivo: o empacotamento dos bits no fluxo de bits corresponde à sua colocação física no chip. Conforme mostrado abaixo, cada bit é armazenado no FPGA próximo ao circuito que ele controla. assim, o formato do arquivo de fluxo de bits é diretamente determinado pela localização dos circuitos de hardware. Por exemplo, se houver um intervalo entre os blocos e um buffer nele, o mesmo intervalo estará no fluxo de bits. A estrutura do fluxo de bits não depende de abstrações de software, como campos em tabelas de dados ou blocos de configuração. Compreender o fluxo de bits requer pensar em termos de hardware, não de software

Bitstream

, (.RBT) , .

, .

, .

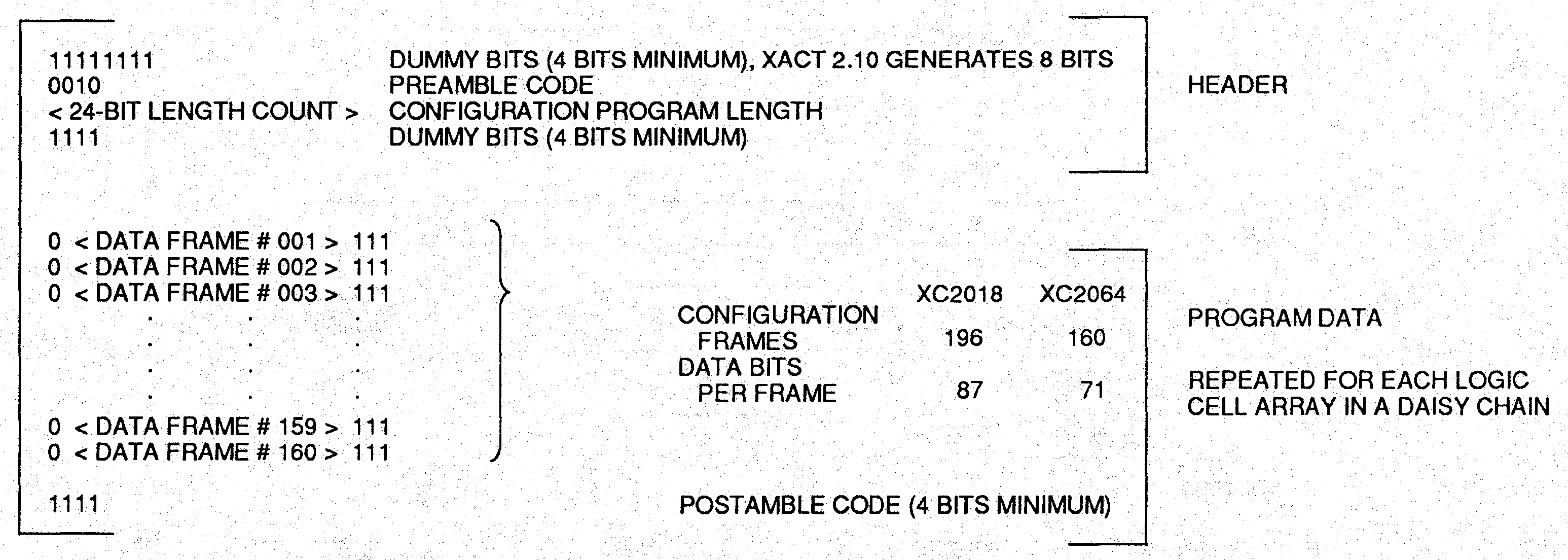

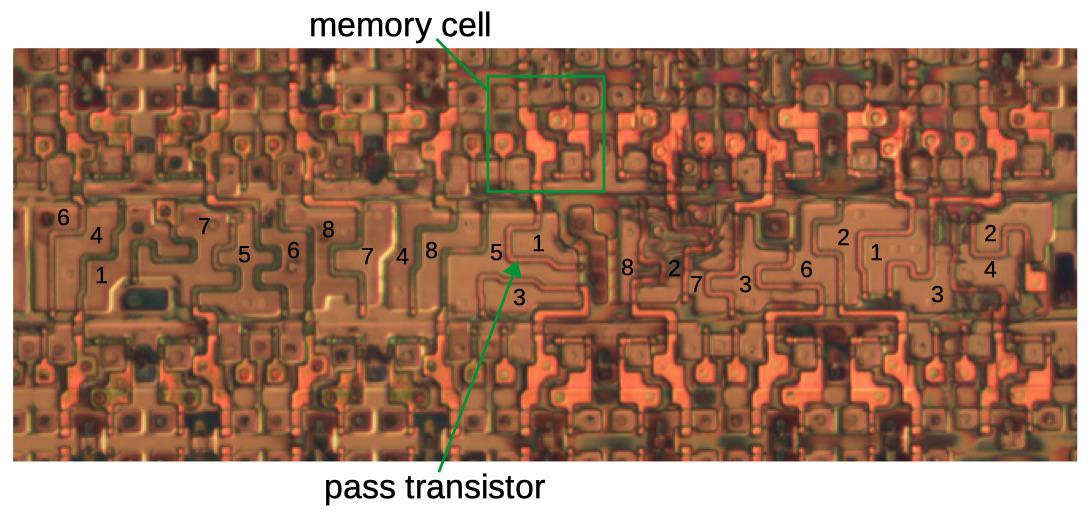

Cada bit de memória de configuração é implementado conforme mostrado abaixo. Cada célula de memória consiste em dois inversores conectados em um loop. tal circuito tem dois estados estáveis e pode armazenar um bit: ou o inversor superior está no estado 1 e o inferior está no estado 0 ou vice-versa. Para escrever em uma célula, o transistor de passagem à esquerda é ativado, passando o sinal. O sinal na linha de dados simplesmente puxa o inversor, escrevendo o bit necessário. (Você também pode ler os dados de configuração usando a mesma linha.) A saída Q e o Q invertido controlam uma função específica no FPGA, como fechar uma rede de interconexão, recuperar um bit de uma tabela de pesquisa ou controlar um acionador. Na maioria dos casos, apenas a saída Q é usada.

Célula SRAM

(SRAM). , RAM, , , SRAM. , 5T SRAM.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

Diagrama de um bit de memória de configuração, da documentação.

A figura abaixo mostra a estrutura física das células de memória. A foto à esquerda mostra 8 células de memória, uma das quais está destacada. Cada linha de dados horizontal é conectada a todos os locais de memória na linha. Cada linha de busca de coluna seleciona todos os locais de memória na coluna, permitindo a escrita. A foto do meio mostra seções de silício e polissilício para uma célula de memória. As camadas de metal foram removidas para expor os transistores embaixo. Camadas de metalização conectam transistores, círculos na foto, que são conexões, vias, entre o silício ou polissilício e o metal. O diagrama mostra como cinco transistores estão conectados, a colocação dos elementos no diagrama corresponde à sua colocação na foto. Dois pares de transistores formam os inversores CMOS, com um transistor de passagem no canto inferior esquerdo fornecendo acesso à célula.

, . — . , . . : siliconpr0n.

Conforme explicado anteriormente, o FPGA implementa funções lógicas arbitrárias usando tabelas de pesquisa. A figura abaixo mostra como a tabela de pesquisa é implementada no XC2064. Os oito valores à esquerda são armazenados em oito locais de memória. Quatro multiplexadores selecionam um de cada par de valores, dependendo do valor na entrada A, se A = 0, o superior dos valores é selecionado, se A = 1, então o inferior. Então, o grande multiplexador escolhe um dos quatro valores com base nos sinais B e C. O resultado será um valor específico, neste caso A XOR B XOR C. Podemos fazer qualquer função lógica se substituirmos valores diferentes na tabela.

Implementação de XOR na tabela de pesquisa.

Cada multiplexador é implementado usando transistores de passagem. Dependendo dos sinais de controle, um dos transistores de passagem é ativado, passando os dados de entrada para saída. A figura abaixo mostra uma parte da cadeia LUT, com dois bits multiplexados. À direita estão dois locais de memória. Cada bit passa pelo inversor, amplificado, e passa pelos transistores de passagem do multiplexador intermediário, selecionando um desses bits.

Vista das redes que implementam o LUT. Retirado do siliconpr0n.

Desencadear

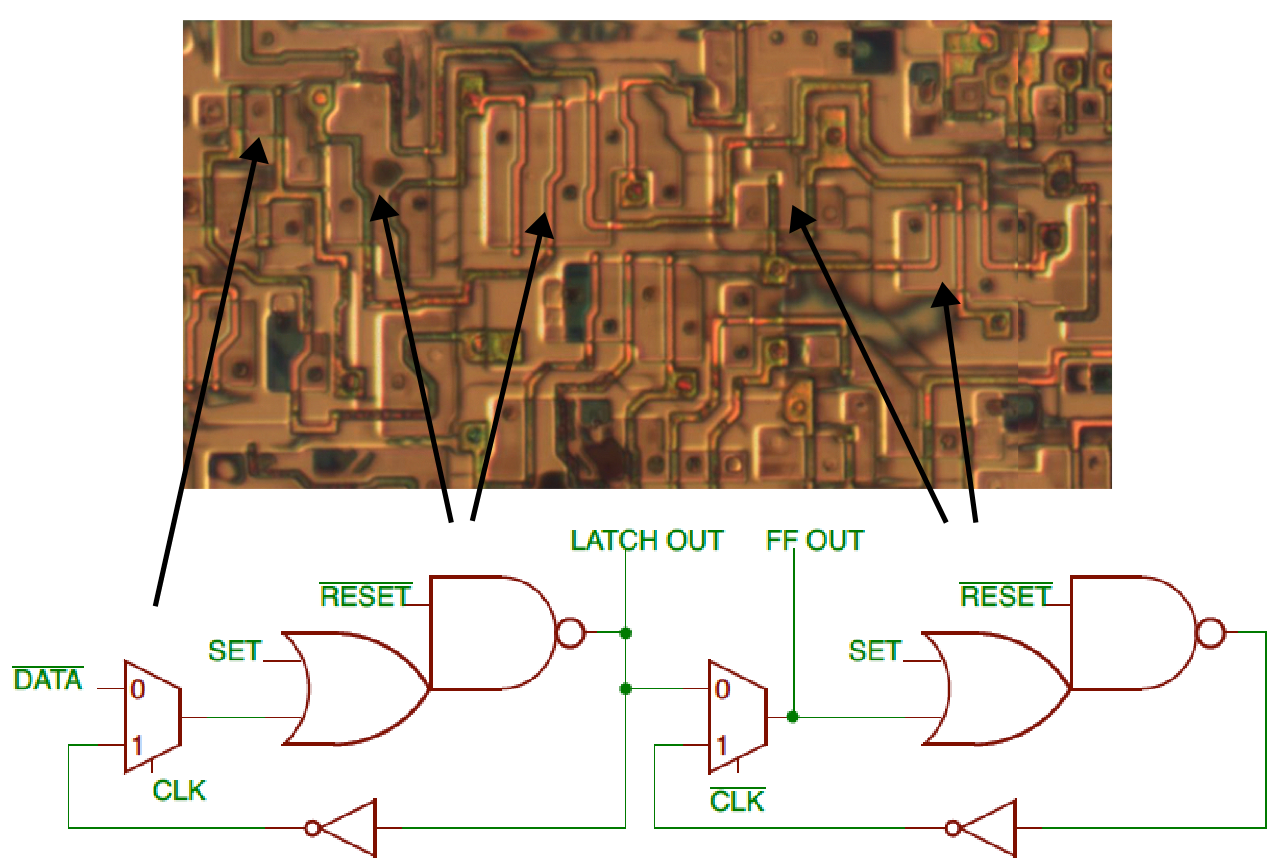

Cada CLB contém um flip-flop que permite ao FPGA implementar latches, máquinas de estado e outras redes com estado. A figura abaixo mostra uma implementação de gatilho (um tanto incomum). Ela usa o seguinte esquema. Quando o sinal do clock é zero, o primeiro mux passa os dados para o primeiro latch, que armazena o valor. O bit é invertido duas vezes, ao passar pelas portas OR, NAND e do inversor, e permanece o mesmo como resultado. além disso, o segundo multiplexador de trava recebe o bit do primeiro trava quando o relógio sobe para 1 (observe que o relógio está invertido). Este valor é a saída do flip-flop. Quando o sinal de clock é definido como 0, o multiplexador secundário fecha o loop travando o bit. Assim, o gatilho é sensível à borda do sinal,travando o valor na borda de ataque do sinal de clock. Definir e redefinir linhas definir e redefinir o flip-flop.

. OR-NAND : siliconpr0n.

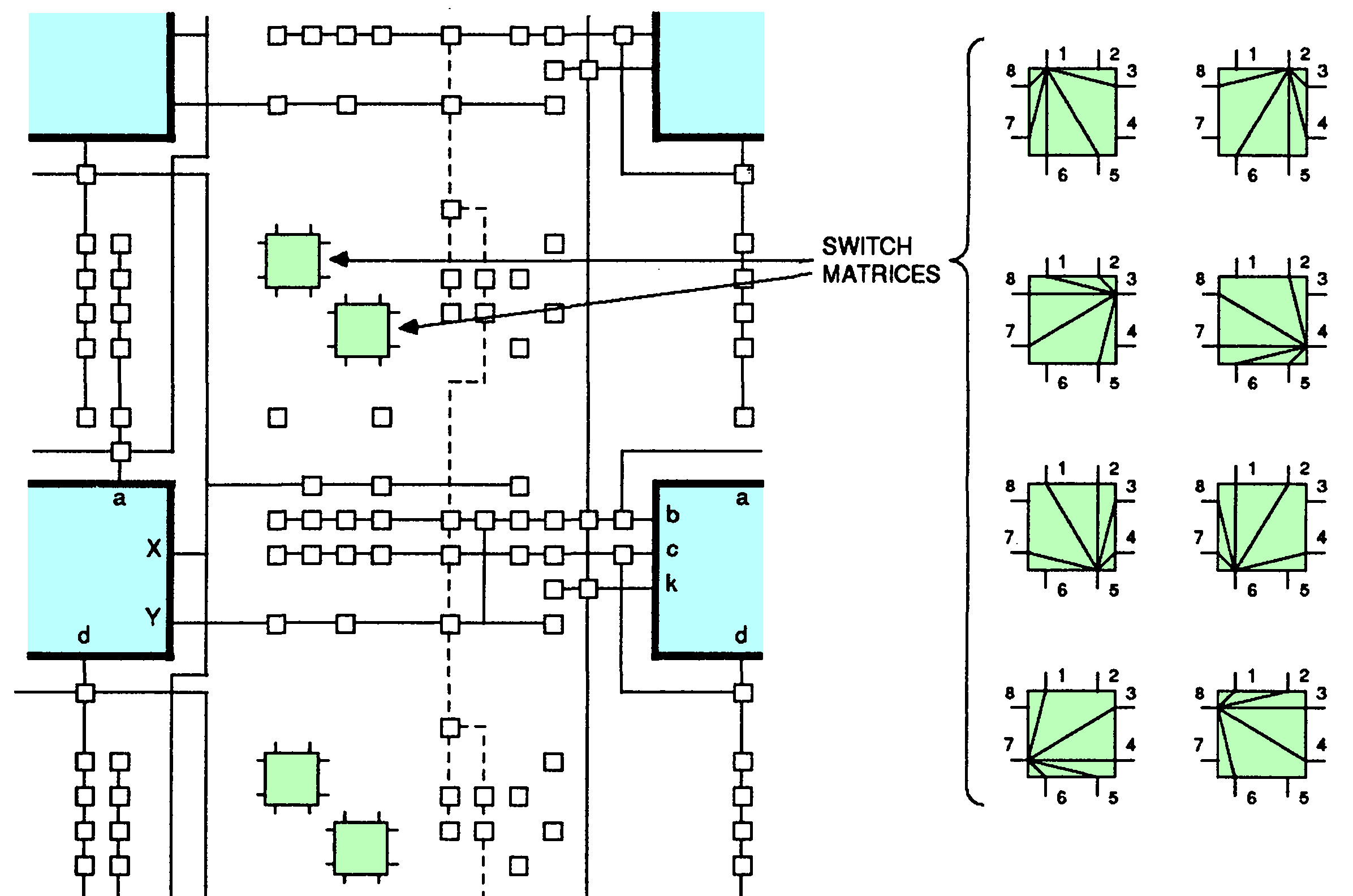

A matriz de switch é um elemento de interconexão importante. Cada switch possui 8 pinos (dois em cada lado) e pode conectá-los de quase todas as formas. Os sinais podem ser desembrulhados, divididos e interceptados com mais flexibilidade do que em nós de interconexão individuais. A figura abaixo mostra uma parte da rede de interconexão entre os quatro CLBs (azul). As matrizes de comutação (verde) podem ser conectadas em qualquer combinação de conexões no lado direito. Observe que cada pino pode ser conectado a outros pinos na quantidade de 5 a 7 peças. Por exemplo, o pino 1 pode ser conectado ao pino 3, mas não aos pinos 2 e 4. Isso torna a matriz quase completa, com 20 conexões possíveis em vez de 28.

Tirado daqui: Livro de dados do array de portas programáveis Xilinx , fig. 7b.

A matriz de comutação é formada por fileiras de transistores de passagem controlados pelas células de memória acima e abaixo delas. Os dois lados do transistor são dois pinos da matriz de comutação que podem ser conectados pelo transistor. Portanto, cada matriz tem 20 bits de controle, duas matrizes por bloco nos dão 40 bits por bloco. A foto abaixo mostra uma célula de memória conectada à porta ondulada do transistor embaixo. Este transistor fornece a conexão entre o pino 5 e o pino 1. Assim, o bit no fluxo de bits correspondente a esta localização da memória controla a conexão entre os pinos 5 e 1. Da mesma forma, outras células de memória e seus transistores associados controlam outras conexões. Observe também que a ordem dessas conexões não segue nenhum padrão particular, como resultado,a correspondência entre os bits no fluxo de bits e os pinos de switch parece aleatória.

Switch Matrix

20 . 18 , .

Implementação de uma matriz de ligações de 8 derivações. As regiões de silício são designadas pelos números de seus pinos correspondentes. As camadas de metal que conectam os condutores correspondentes aos transistores foram removidas. Retirado do siliconpr0n.

Conexões de entrada

As entradas CLB usam um esquema de codificação de fluxo de bits diferente, que é explicado por sua implementação de hardware. Na imagem abaixo, os oito nós reticulados são entradas potenciais para o CLB chamado DD. Apenas um nó (máximo) pode ser configurado como entrada, já que conectar dois sinais a uma entrada pode colocá-los em curto.

Seleção de entrada. As oito entradas circuladas em verde são entradas DD potenciais, apenas uma delas pode ser selecionada.

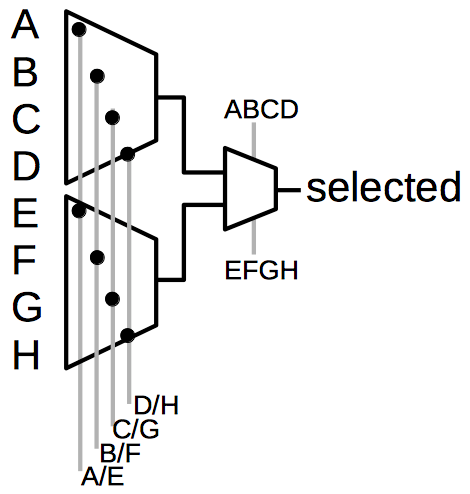

A entrada necessária é selecionada pelo multiplexador. Uma solução direta seria usar um multiplexador de 8 entradas com três bits de controle, escolhendo um dos 8 sinais. Outra solução direta seria usar transistores de 8 passagens, cada um com seu próprio sinal de controle, um dos quais seleciona o sinal necessário. No entanto, o FPGA usa uma abordagem híbrida que elimina a necessidade de um decodificador no primeiro caso, mas requer 5 sinais de controle em vez dos 8 exigidos na segunda abordagem.

O FPGA usa multiplexadores para selecionar uma das oito entradas.

O diagrama na figura acima mostra o multiplexador de duas camadas usado no FPGA. No primeiro estágio, um dos sinais de controle é ativado. No segundo estágio, o sinal alto ou baixo é selecionado e aplicado à saída. Por exemplo, suponha que o sinal de controle B / F seja aplicado ao primeiro estágio e ABCD ao segundo estágio, a entrada B será a única que vai para a saída. Ou seja, selecionar uma das oito entradas requer 5 bits no fluxo de bits e usa 5 locais de memória.

Multiplexador de entrada CLB

CLB. EFGH ABCD, . -, CLB 6 10 , , . , , , , . , , 6 , . , , .

Conclusão

O XC2064 usa uma variedade de redes altamente otimizadas para implementar blocos lógicos e interconexões de rede. Essas correntes precisam ser bem embaladas para caber no cristal. Mesmo assim, o XC2064 era um chip muito grande, maior que o microprocessador da época, e de difícil fabricação, custando centenas de dólares. Comparado aos FPGAs modernos, o XC2064 tem um número absurdamente pequeno de células, mas mesmo assim foi o início de uma nova linha de produtos revolucionária.

Dois conceitos são essenciais para entender o fluxo de bits XC2064. Primeiro, o FPGA é implementado com base em 64 tiles, blocos repetidos que combinam blocos lógicos e interconexões. Embora o FPGA seja descrito como tendo blocos lógicos cercados por interconexões, ele não é implementado dessa forma. O segundo conceito é que o fluxo de bits não é baseado em nenhuma abstração, ele mapeia diretamente o empacotamento bidimensional das células de memória FPGA. Portanto, bitstream só faz sentido se você estiver considerando a estrutura física do FPGA.

Nota

, XC2064 (. 11), CLB . , , 20% , . — -, . , . .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

Eu anunciei meu último post no twitter, então siga kenshirriff . Eu também tenho um feed RSS . Agradecimentos a John McMaster, Tim Ansell e Philip Freidin pelas discussões.