Todas as unidades centrais de processamento de qualquer computador, seja um laptop barato ou um servidor de milhões de dólares, têm um dispositivo chamado cache. E com uma probabilidade muito alta tem vários níveis.

Provavelmente é importante, caso contrário, por que instalá-lo? Mas o que o cache faz e por que ele tem níveis diferentes? E o que significa "conjunto associativo de 12 vias"?

O que é cache?

TL; DR: Esta é uma memória pequena, mas muito rápida, localizada nas proximidades dos blocos lógicos da CPU.

No entanto, podemos aprender muito mais sobre o cache ...

Vamos começar com um sistema de armazenamento mágico imaginário: é infinitamente rápido, pode lidar com um número infinito de transferências de dados ao mesmo tempo e sempre fornece armazenamento de dados seguro e confiável. Claro, nada desse tipo existe por perto, mas se fosse assim, a estrutura do processador seria muito mais simples.

Os processadores então precisariam apenas de blocos lógicos para adição, multiplicação, etc., bem como um sistema de controle de transmissão de dados, porque nosso sistema de armazenamento teórico é capaz de transmitir e receber instantaneamente todos os números necessários; nenhum bloco lógico precisa ficar ocioso enquanto espera pela transferência dos dados.

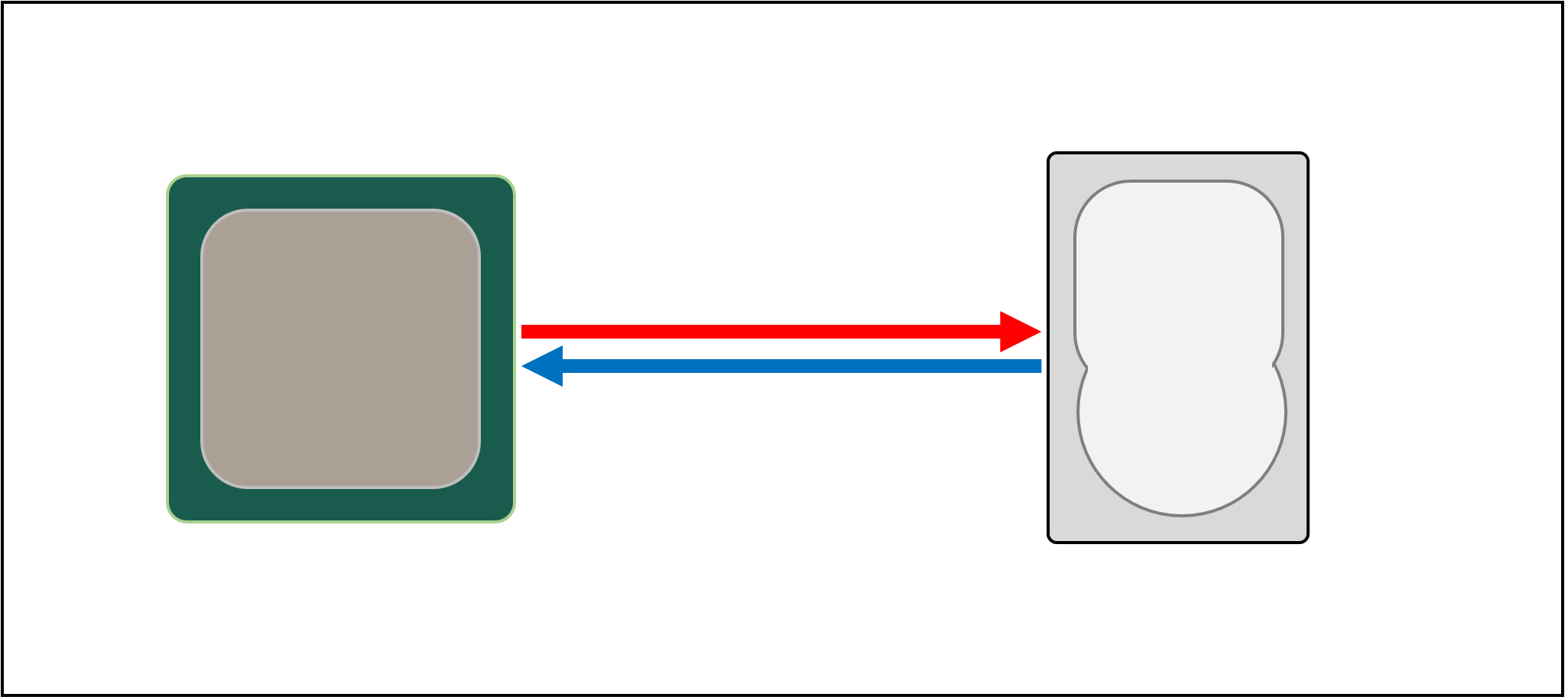

Mas, como sabemos, não existe essa tecnologia de armazenamento mágico. Em vez disso, temos discos rígidos ou unidades de estado sólido e mesmo os melhores deles ficam muito aquém dos recursos de processamento exigidos de um processador moderno.

O grande t'Fon do armazenamento

A razão para isso é que os processadores modernos são incrivelmente rápidos - eles só precisam de um ciclo de clock para adicionar dois inteiros de 64 bits; se o processador está funcionando a 4 GHz, isso é apenas 0,00000000025 segundos ou um quarto de nanossegundo.

Ao mesmo tempo, um disco rígido em rotação leva milhares de nanossegundos apenas para localizar os dados nos discos, sem falar na transferência deles, e as unidades de estado sólido levam dezenas ou centenas de nanossegundos.

Obviamente, essas unidades não podem ser construídas dentroprocessadores, então haverá uma separação física entre eles. Portanto, acrescenta-se tempo para mover os dados, o que agrava a situação.

Infelizmente, este é o Grande A'Tuin do armazenamento de dados.

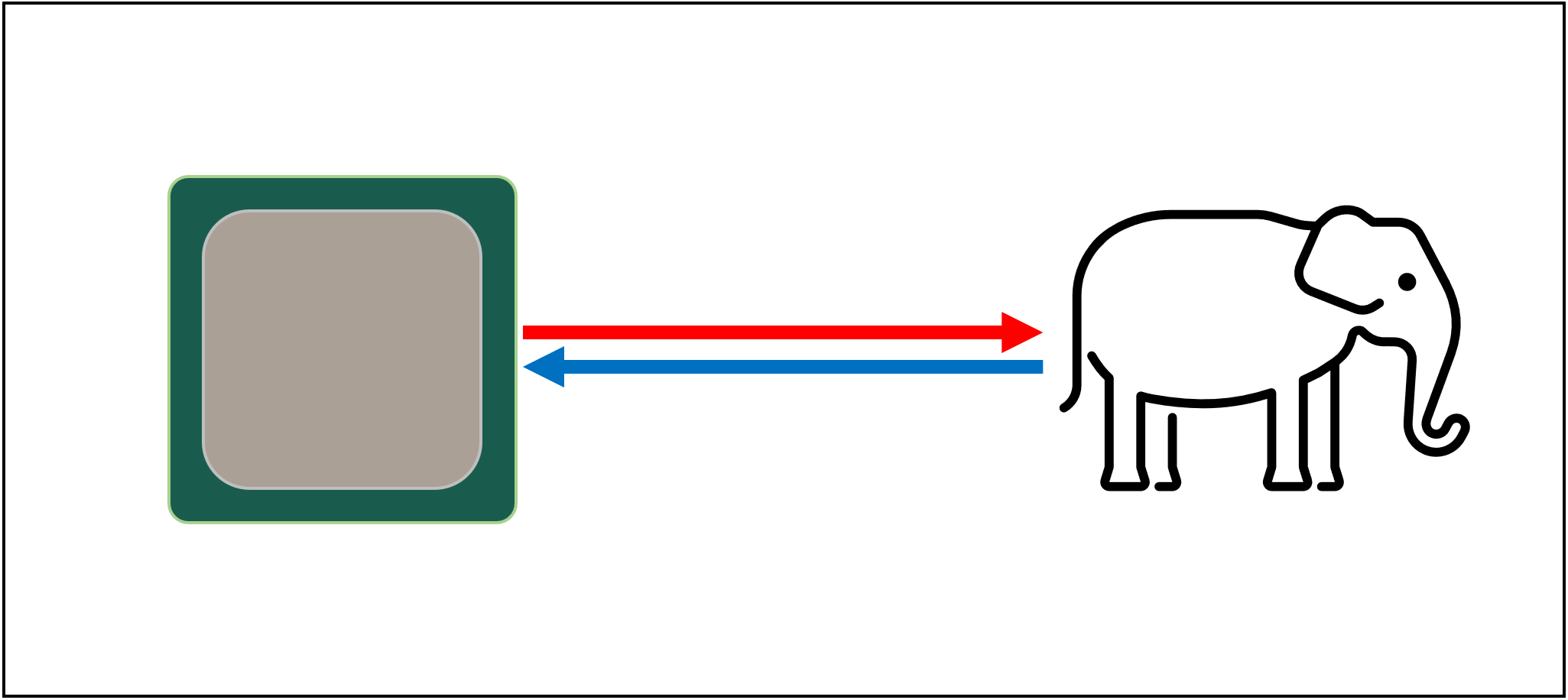

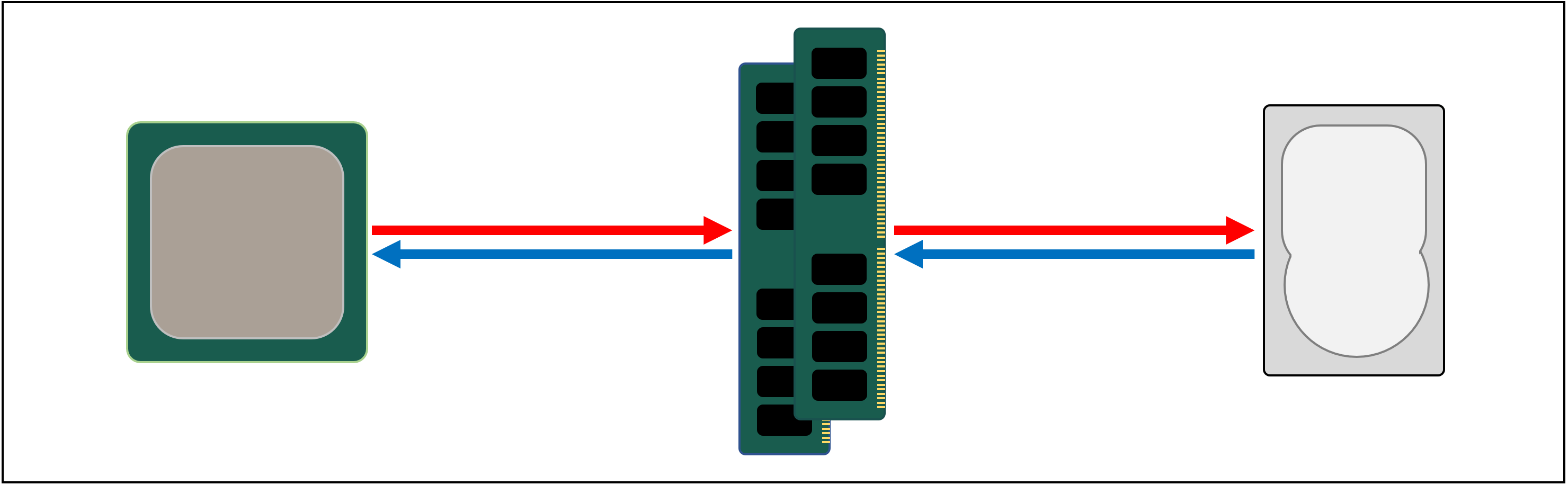

É por isso que precisamos de outro sistema de armazenamento localizado entre o processador e a unidade principal. Deve ser mais rápido que um dispositivo de armazenamento, capaz de lidar com várias transferências de dados simultaneamente e estar muito mais próximo do processador.

Bem, já temos esse sistema, e é chamado de RAM ; ele está presente em todos os computadores e executa exatamente essa tarefa.

Quase todos esses armazenamentos são do tipo DRAM (memória dinâmica de acesso aleatório) ; eles são capazes de transferir dados muito mais rápido do que qualquer dispositivo de armazenamento.

No entanto, apesar de sua enorme velocidade, a DRAM não é capaz de armazenar tais quantidades de dados.

Alguns dos maiores chips de memória DDR4 desenvolvidos pela Micron armazenam 32 Gb, ou 4 GB de dados; os maiores discos rígidos armazenam 4.000 vezes mais.

Portanto, embora tenhamos aumentado a velocidade de nossa rede de dados, precisaremos de sistemas adicionais (hardware e software) para descobrir quais dados devem ser armazenados em uma quantidade limitada de DRAM, pronta para processamento pelo processador.

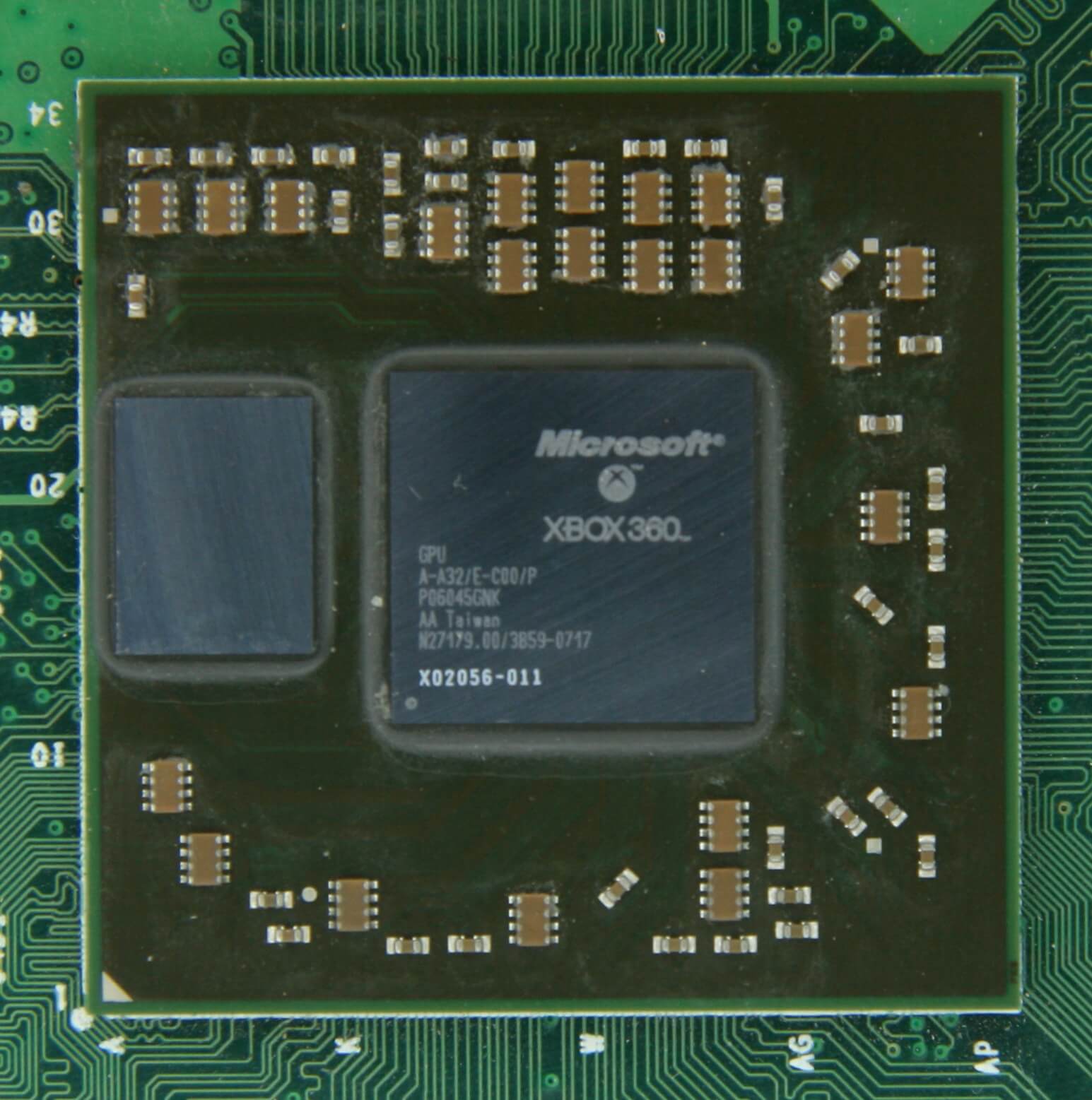

A DRAM pode ser fabricada em um pacote de chips (isso é chamado de DRAM embutida). No entanto, os processadores são muito pequenos, por isso não cabem muita memória.

10 MB DRAM à esquerda da GPU do Xbox 360. Fonte: CPU Grave Yard

A grande maioria da DRAM está localizada nas proximidades do processador, conectada à placa-mãe e é sempre o componente mais próximo do processador. No entanto, essa memória ainda não é rápida o suficiente ...

DRAM leva cerca de 100 nanossegundos para encontrar os dados, mas pelo menos é capaz de transferir bilhões de bits por segundo. Parece que precisamos de outro estágio de memória que pode ser colocado entre os blocos de CPU e DRAM.

O estágio restante aparece em cena: SRAM ( memória de acesso aleatório estática) A DRAM usa capacitores microscópicos para armazenar dados na forma de carga elétrica, enquanto a SRAM usa transistores para a mesma tarefa, que operam na mesma velocidade que os blocos lógicos do processador (cerca de 10 vezes mais rápido que a DRAM).

Obviamente, SRAM tem uma desvantagem e, novamente, tem a ver com espaço.

A memória do transistor ocupa muito mais espaço do que a DRAM: com o mesmo tamanho de um chip DDR4 de 4 GB, você pode obter menos de 100 MB de SRAM. Mas, como é fabricado usando o mesmo processo de fabricação da CPU, a SRAM pode ser embutida diretamente no processador, o mais próximo possível dos blocos lógicos.

A cada etapa adicional, aumentamos a velocidade dos dados transferidos ao custo do volume armazenado. Podemos prosseguir e adicionar novas etapas, que serão mais rápidas, porém menores.

E assim chegamos a uma definição mais estritaconceitos de cache: uma coleção de SRAMs localizada dentro do processador; eles maximizam a utilização do processador, transferindo e armazenando dados em velocidades muito altas. Você está satisfeito com esta definição? Ótimo, porque tudo vai ficar muito mais complicado de agora em diante!

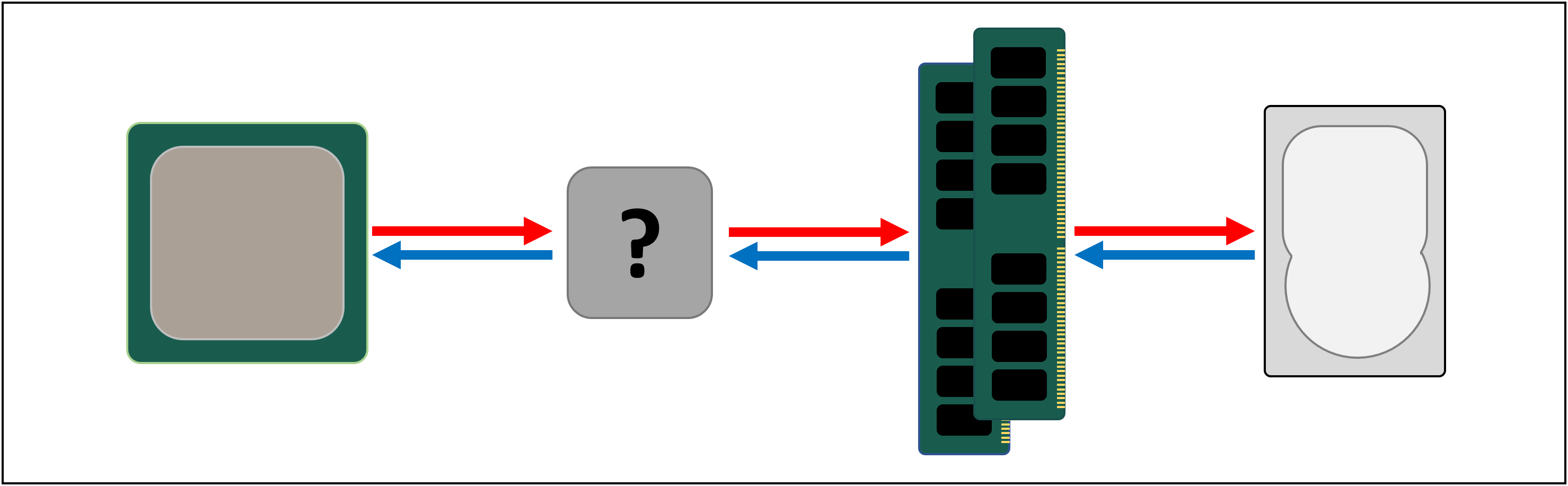

Dinheiro: estacionamento multinível

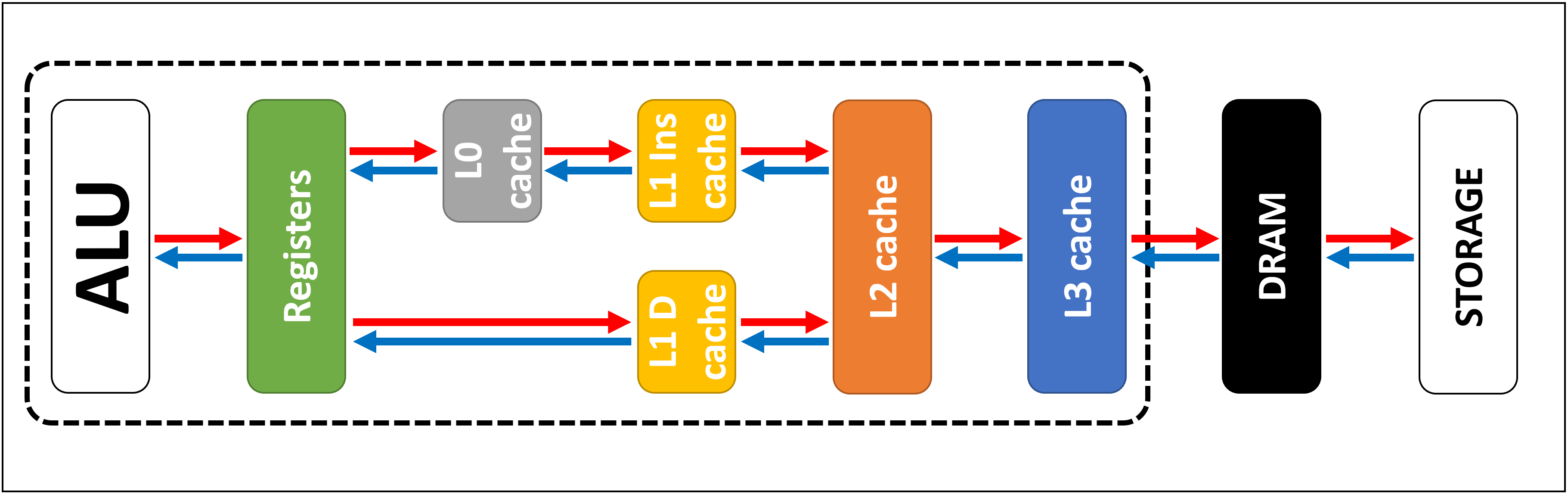

Como dissemos acima, o cache é necessário porque não temos um sistema de armazenamento mágico que consiga lidar com o consumo de dados dos blocos lógicos do processador. CPUs e GPUs modernas contêm muitas SRAMs, organizadas em uma hierarquia - uma sequência de caches com a seguinte estrutura:

Na imagem acima, o processador (CPU) é indicado por um retângulo pontilhado. À esquerda estão as ALUs (unidades lógicas aritméticas); são estruturas que realizam operações matemáticas. Embora não seja estritamente um cache, o nível de memória mais próximo da ALU são os registros (eles são ordenados em um arquivo de registro ).

Cada um deles armazena um número, por exemplo, um inteiro de 64 bits; o próprio valor pode ser um elemento de alguns dados, um código de uma instrução específica ou um endereço de memória de alguns outros dados.

O arquivo de registro em processadores desktop é bastante pequeno, por exemplo, em cada um dos núcleos Intel Core i9-9900Kexistem dois bancos desses arquivos, e o dos inteiros contém apenas 180 inteiros de 64 bits. Outro arquivo de registro para vetores (pequenas matrizes de números) contém 168 elementos de 256 bits. Ou seja, o arquivo de registro total para cada núcleo é ligeiramente inferior a 7 KB. Para comparação, o arquivo de registro Nvidia GeForce RTX 2080 Ti para streaming de multiprocessadores (como as GPUs chamam de análogos de núcleo de CPU) tem 256 KB de tamanho.

Os registros, como o cache, são SRAMs, mas sua velocidade não excede a velocidade das ALUs que atendem; eles transferem dados em um ciclo de clock. Mas eles não são projetados para armazenar grandes quantidades de dados (apenas um elemento), então sempre há blocos maiores de memória ao lado deles: este é o cache de primeiro nível (Nível 1).

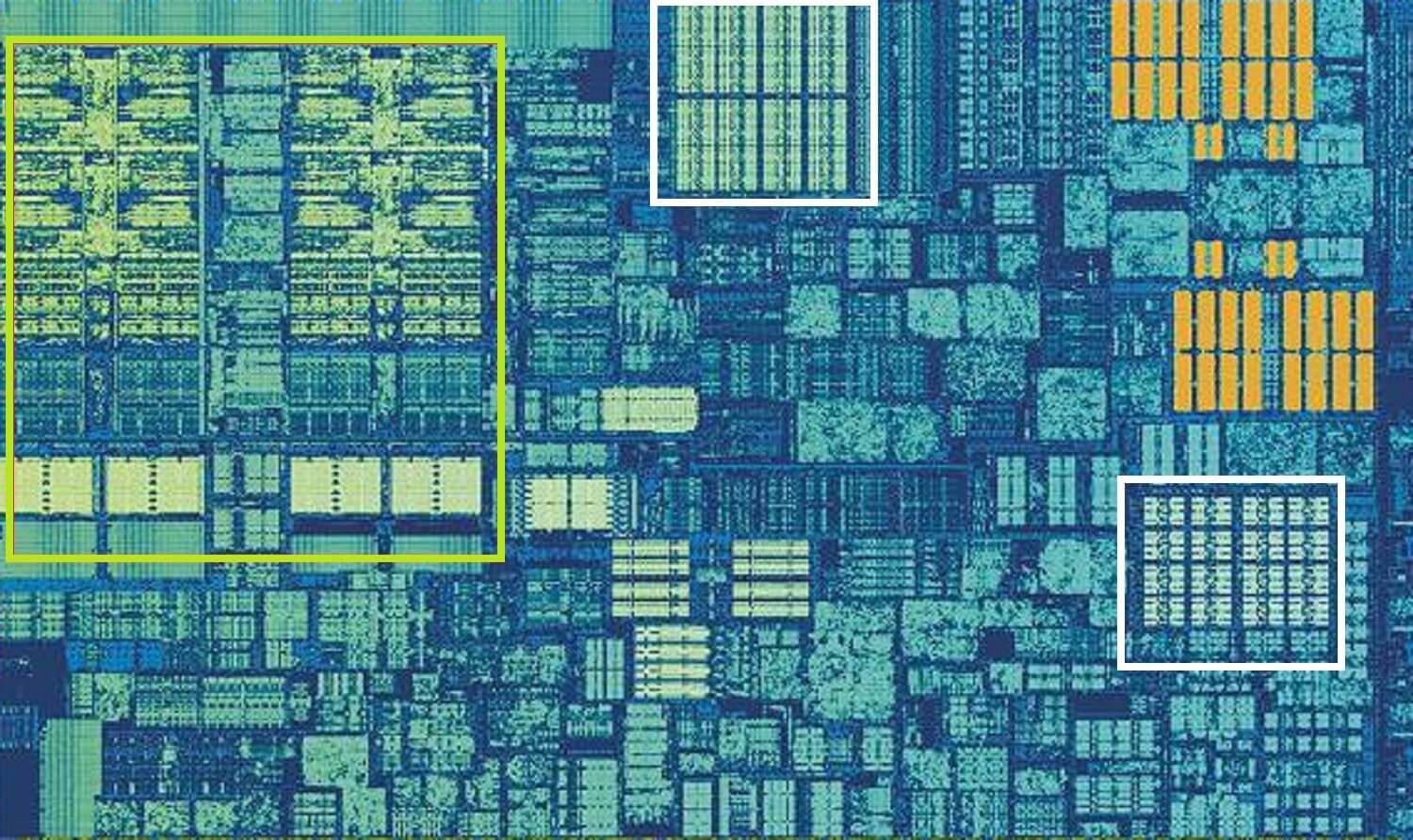

Um núcleo de processador Intel Skylake. Fonte: Wikichip

A imagem acima é uma visão ampliada de um dos núcleos do processador Intel Skylake para desktop .

Os arquivos ALU e de registro estão localizados à esquerda e são circundados por um quadro verde. Na parte superior da foto, o cache de dados de nível 1 é indicado em branco. Não contém muita informação, apenas 32 KB, mas como os registradores, está localizado muito próximo aos blocos lógicos e opera na mesma velocidade que eles.

Outro retângulo branco à direita mostra o cache de instrução de nível 1, também de 32 KB. Como o nome indica, ele armazena vários comandos prontos para serem divididos em micro-operações menores .(geralmente denotado por μops) que as ALUs devem executar. Também existe um cache para eles, que pode ser classificado como Nível 0, por ser menor (contém apenas 1.500 operações) e mais próximo que os caches L1.

Você pode estar se perguntando por que essas SRAMs são tão pequenas? Por que eles não têm megabytes de tamanho? Juntos, os caches de dados e instruções ocupam quase a mesma área no chip que os blocos lógicos principais, então seu aumento levará a um aumento na área total do dado.

Mas a principal razão para o tamanho de vários kilobytes é que, conforme a capacidade da memória aumenta, o tempo necessário para pesquisar e recuperar os dados aumenta. O cache L1 precisa ser muito rápido, então há uma compensação entre tamanho e velocidade - na melhor das hipóteses, leva cerca de 5 ciclos de clock para obter dados deste cache (mais para valores de ponto flutuante).

Cache L2 do Skylake: 256KB SRAM

Mas se este fosse o único cache dentro do processador, seu desempenho enfrentaria um obstáculo inesperado. É por isso que outra camada de memória é construída nos kernels: o cache de nível 2. Este é um bloco de armazenamento generalizado que contém instruções e dados.

É sempre maior do que o Nível 1: nos processadores AMD Zen 2 , leva até 512 KB para fornecer dados suficientes para caches de nível inferior. No entanto, o tamanho grande requer sacrifício - leva cerca de duas vezes mais tempo para localizar e transferir dados deste cache em comparação com o Nível 1.

Na época do primeiro Intel Pentium, o cache de Nível 2 era um chip separado, instalado em uma pequena placa separada (como DIMM RAM) ou embutido na placa-mãe principal. Gradualmente, ele se mudou para a caixa do próprio processador e, finalmente, foi totalmente integrado ao cristal do chip; isso aconteceu na era de processadores como o Pentium III e AMD K6-III.

Essa conquista foi logo seguida por outro nível de cache necessário para suportar níveis mais baixos, e chegou bem a tempo para o apogeu dos chips multi-core.

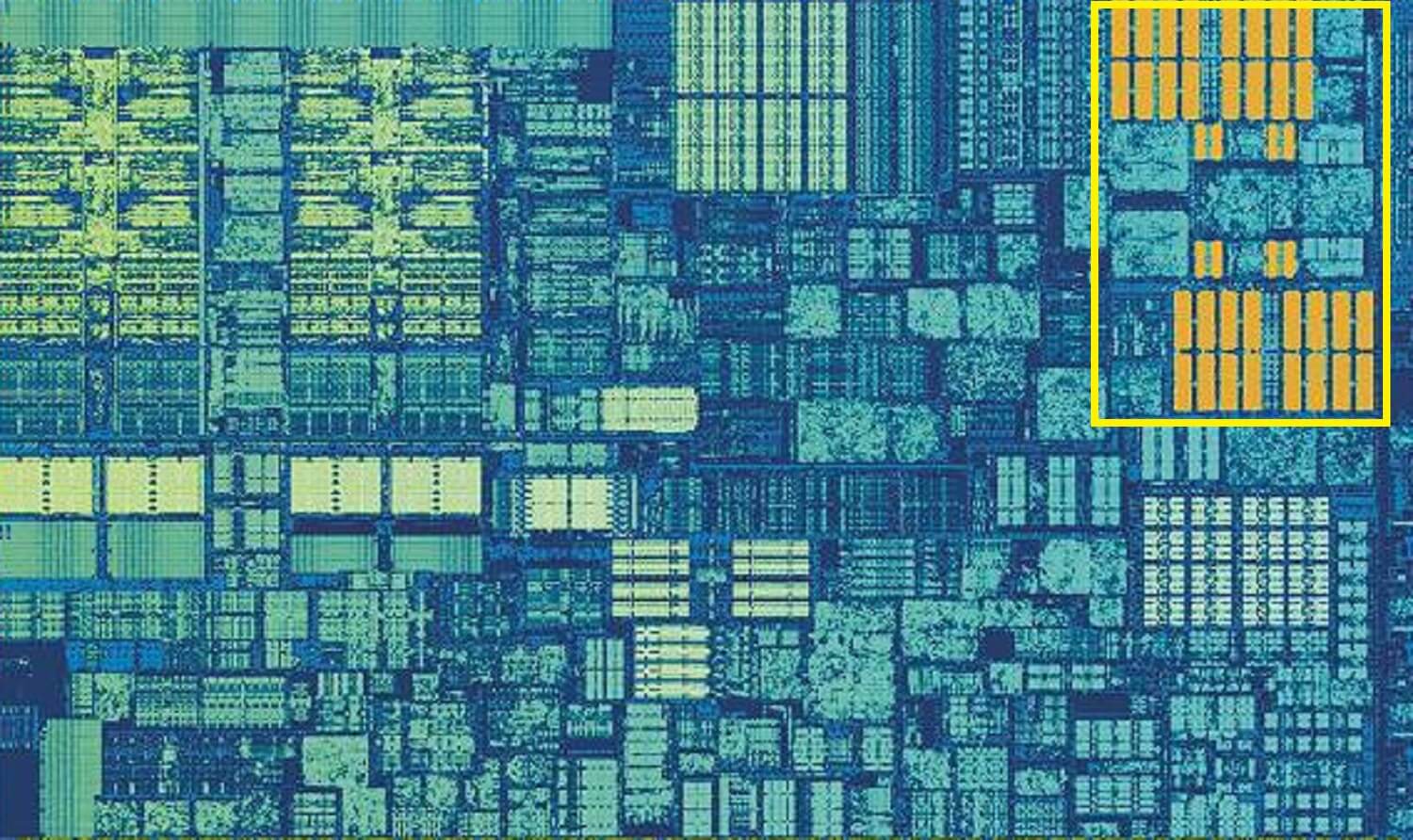

Chip Intel Kaby Lake. Fonte: Wikichip

Esta imagem do chip Intel Kaby Lake mostra quatro núcleos à esquerda (a GPU integrada ocupa quase a metade do dado e está à direita). Cada núcleo tem seu próprio conjunto "pessoal" de caches de Nível 1 e 2 (destacados em caixas brancas e amarelas), mas eles também têm um terceiro conjunto de blocos SRAM.

O cache de terceiro nível (Nível 3), embora localizado diretamente próximo a um núcleo, é completamente comum a todos os outros - cada núcleo pode acessar livremente o conteúdo do cache L3 de outro núcleo. É muito maior (2 a 32 MB), mas também muito mais lento, com média de mais de 30 ciclos, especialmente quando o kernel precisa usar dados que residem em um bloco de cache distante.

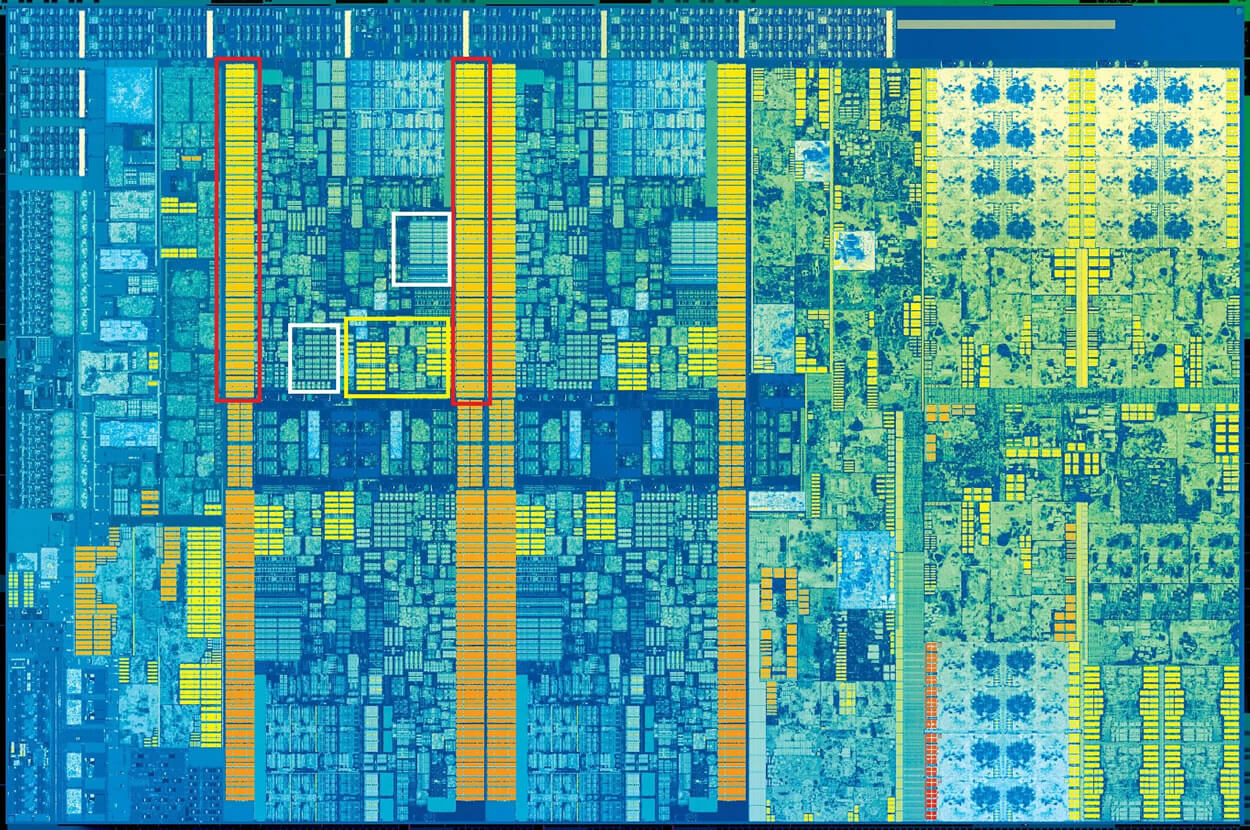

Abaixo, é mostrado um núcleo da arquitetura AMD Zen 2: caches de dados e instruções de 32 KB Nível 1 (em caixas brancas), cache de 512 KB Nível 2 (em caixas amarelas) e um enorme bloco de cache L3 de 4 MB (em caixa vermelha).

Ampliado em um único núcleo de um processador AMD Zen 2. Fonte: Fritzchens Fritz

Mas espere: como 32 KB pode ocupar mais espaço físico do que 512 KB? Se o Nível 1 armazena tão poucos dados, por que é desproporcionalmente grande em comparação com os caches L2 e L3?

Não apenas números

O cache melhora o desempenho ao acelerar a transferência de dados para blocos lógicos e manter por perto uma cópia de instruções e dados usados com frequência. As informações armazenadas no cache são divididas em duas partes: os próprios dados e o local onde estão originalmente localizados na memória / armazenamento do sistema - esse endereço é denominado tag de cache .

Quando o processador executa uma operação que precisa ler ou gravar dados de / para a memória, ele começa verificando as tags no cache de Nível 1. Se os dados necessários estiverem lá (ocorreu um acerto de cache ), então esses dados estão quase De uma vez só. Uma falha de cache ocorre quando a tag necessária não é encontrada no nível mais baixo do cache.

Um novo tag é criado no cache L1 e o resto da arquitetura do processador assume, procurando em outros níveis do cache (até o armazenamento principal, se necessário) os dados para aquele tag. Mas para liberar espaço no cache L1 para essa nova tag, algo deve ser colocado em L2.

Isso resulta em um embaralhamento quase constante de dados, executado em apenas alguns ciclos de clock. A única maneira de conseguir isso é criando uma estrutura complexa em torno da SRAM para lidar com o gerenciamento de dados. Em outras palavras, se o núcleo do processador consistisse em apenas uma ALU, o cache L1 seria muito mais simples, mas como existem dezenas deles (e muitos deles fazem malabarismos com dois fluxos de instrução), o cache requer muitas conexões para mover os dados.

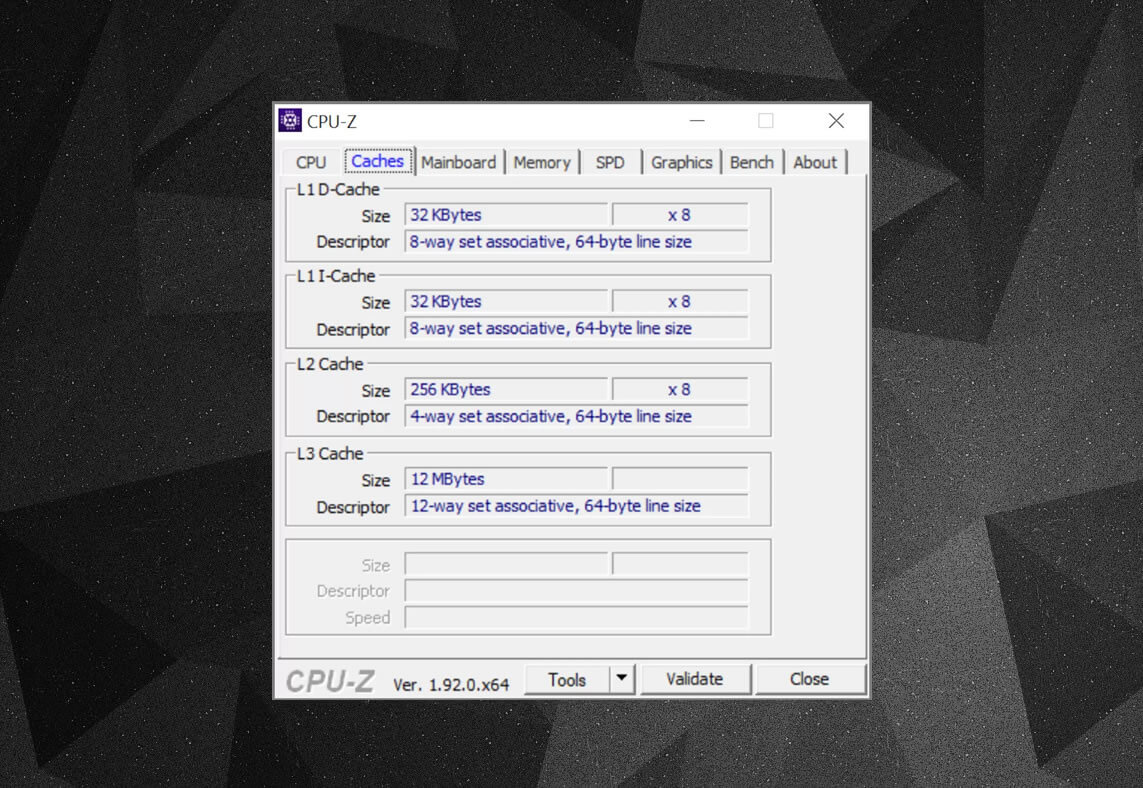

Você pode usar programas gratuitos como o CPU-Z para examinar as informações do cache no processador do seu computador . Mas o que todas essas informações significam? Um elemento importante é o rótulo associativo definido , que indica as regras usadas para copiar blocos de dados da memória do sistema para o cache.

As informações de cache acima são para Intel Core i7-9700K . Cada um de seus caches de Nível 1 é dividido em 64 pequenos blocos, chamados conjuntos , e cada um desses blocos também é dividido em linhas de cache.(Tamanho de 64 bytes). "Conjunto associativo" significa que um bloco de dados do sistema está vinculado a linhas de cache em um conjunto específico e não pode ser vinculado livremente a outro lugar.

"8 vias" significa que um bloco pode ser associado a 8 linhas de cache no conjunto. Quanto mais alto o nível de associatividade (ou seja, quanto maior o “caminho”), mais chances de um cache acertar durante uma consulta ao processador e menos perda causada por falhas de cache. As desvantagens de tal sistema são o aumento da complexidade e do consumo de energia, bem como o baixo desempenho, porque mais linhas de cache devem ser processadas para cada bloco de dados.

Cache inclusivo L1 + L2, cache de vítima L3, políticas de write-back, há até ECC. Fonte: Fritzchens Fritz

Outro aspecto da complexidade do cache tem a ver com como os dados são armazenados entre as diferentes camadas. As regras são definidas na política de inclusão . Por exemplo, os processadores Intel Core têm caches L1 + L3 totalmente inclusivos . Isso significa que alguns dados no Nível 1, por exemplo, podem estar presentes no Nível 3. Pode parecer um desperdício de espaço valioso do cache, mas a vantagem é que se o processador perder a tag no nível inferior, ele não precisa pesquise dados de nível superior.

Nos mesmos processadores, o cache L2 não é inclusivo: todos os dados armazenados nele não são copiados para nenhuma outra camada. Isso economiza espaço, mas faz com que o sistema de memória do chip procure uma tag ausente em L3 (que é sempre muito maior). Os caches de vítimas são semelhantes em princípio, mas são usados para armazenar informações transportadas de níveis inferiores. Por exemplo, os processadores AMD Zen 2 usam o cache de vítima L3, que simplesmente armazena dados de L2.

Existem outras políticas de cache, como gravar dados no cache e na memória principal do sistema. Elas são chamadas de políticas de gravação ; a maioria dos processadores modernos usa caches write-back- isso significa que quando os dados são gravados na camada de cache, há um atraso antes de gravar uma cópia deles na memória do sistema. Na maioria das vezes, essa pausa dura enquanto os dados permanecem no cache - a RAM recebe essas informações apenas quando são "retiradas" do cache.

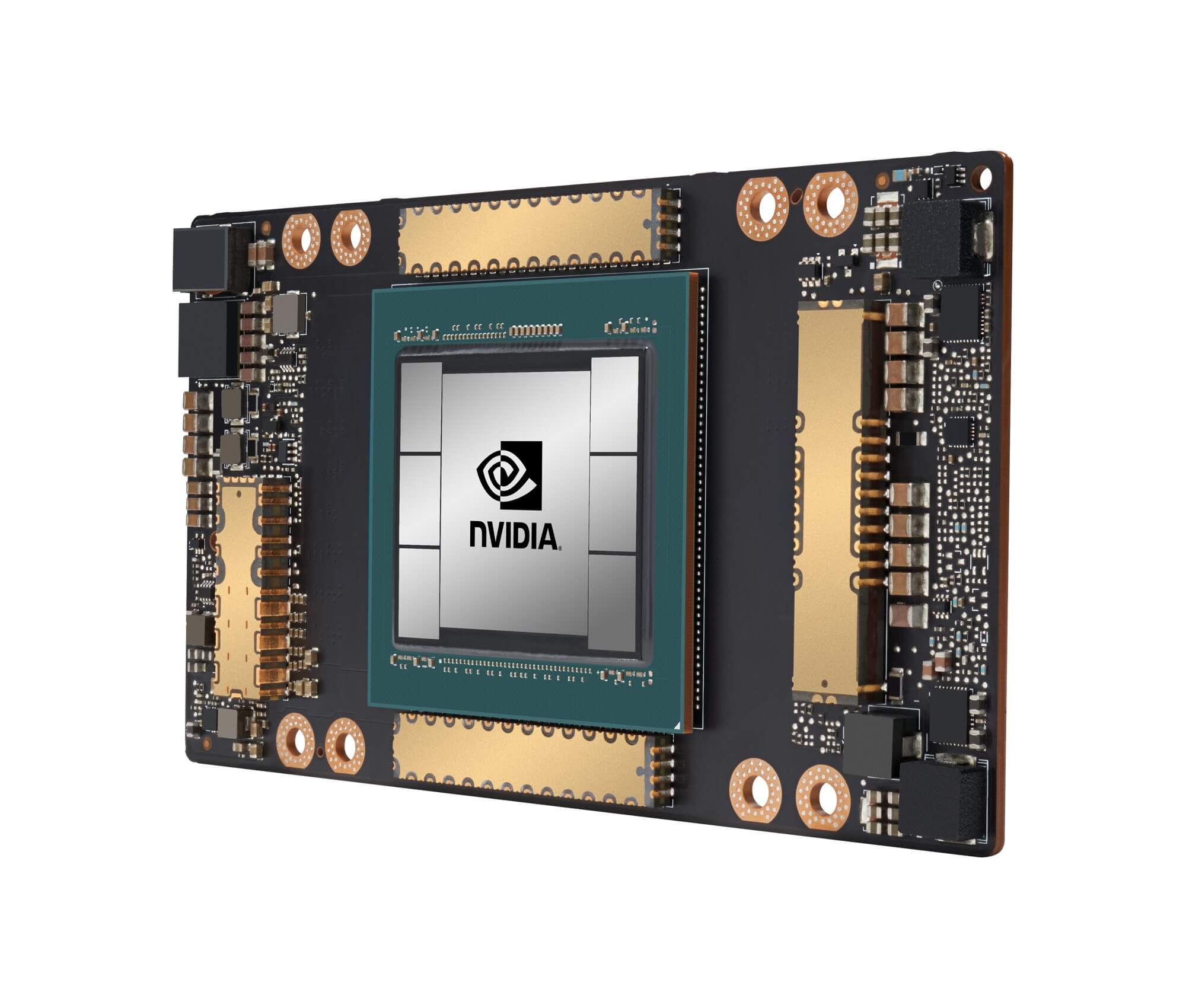

GPU Nvidia GA100 com cache L1 de 20 MB e cache L2 de 40 MB

Para designers de processadores, a escolha do tamanho, tipo e política do cache é uma questão de equilibrar a unidade para aumentar a potência do processador com o aumento da complexidade e do espaço do chip. Se fosse possível criar caches associativos de 20 MB Nível 1 de 1000 canais de modo que eles não ocupassem a área de Manhattan (e não consumissem a mesma quantidade de energia), então todos teríamos computadores com esses chips!

O nível mais baixo de caches nos processadores modernos permaneceu quase inalterado na última década. No entanto, o cache de Nível 3 continua crescendo em tamanho. Se você tivesse US $ 999 em um Intel i7-980X dez anos atrás, poderia obter um cache de 12 MB. Hoje por metade dessa quantiadisponível para compra 64 MB .

Para resumir, o cache é um dispositivo absolutamente essencial e incrível. Não cobrimos outros tipos de caches na CPU e GPU (por exemplo, buffers de tradução associativa ou caches de textura), mas como todos eles têm a mesma estrutura simples e layout de níveis, não será difícil entendê-los.

Você já teve um computador com cache L2 na placa-mãe? Que tal placas- filha com fenda Pentium II e Celeron (por exemplo, 300a )? Lembra do seu primeiro processador L3 compartilhado?

Publicidade

Nossa empresa oferece aluguel de servidores com processadores Intel e AMD. No último caso, esses são servidores épicos! VDS com AMD EPYC , frequência do núcleo da CPU de até 3,4 GHz. A configuração máxima é de 128 núcleos de CPU, 512 GB de RAM, 4000 GB NVMe.